# MOSTEK MICROCOMPUTER 3870/F8 DATA BOOK

# **MICROCOMPUTER 3870/F8 DATA BOOK INDEX**

# 3870 DATA SHEETS

| MK3870 | Single-Chip Microcomputer  |

|--------|----------------------------|

| MK3872 | Single-Chip Microcomputer  |

| MK3876 | Single-Chip Microcomputer6 |

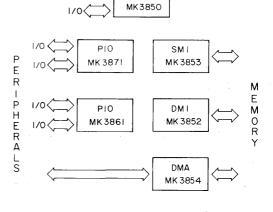

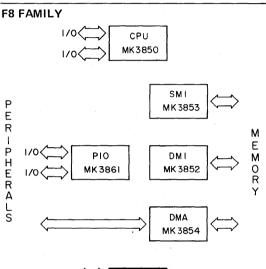

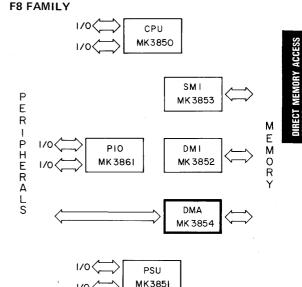

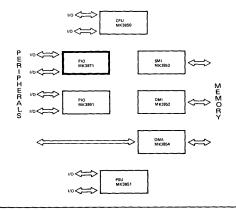

# **F8 DATA SHEETS**

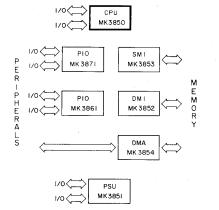

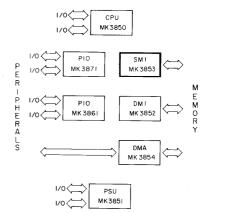

| MK3850<br>MK3851 | F8 Central Processing Unit |   |

|------------------|----------------------------|---|

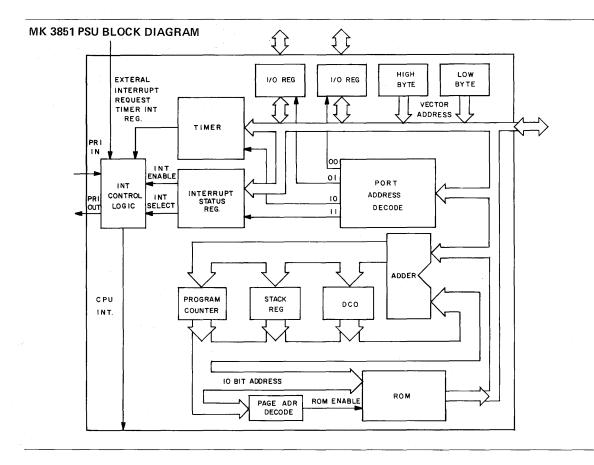

| MK3851<br>MK3852 | Program Storage Unit       | 7 |

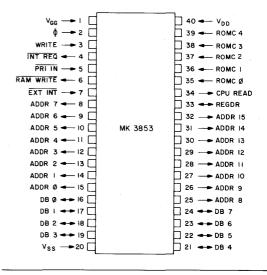

| MK3853<br>MK3854 | Static Memory Interface    |   |

| MK3861<br>MK3871 | Peripheral Input/Output    |   |

# 3870/F8 SYSTEM DOCUMENTATION

229

271

281

1

101

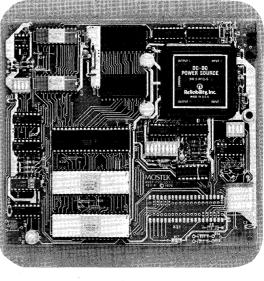

| MCK-50/70  | Evaluation Kit                      | 1 |

|------------|-------------------------------------|---|

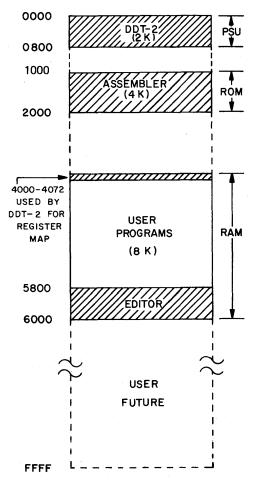

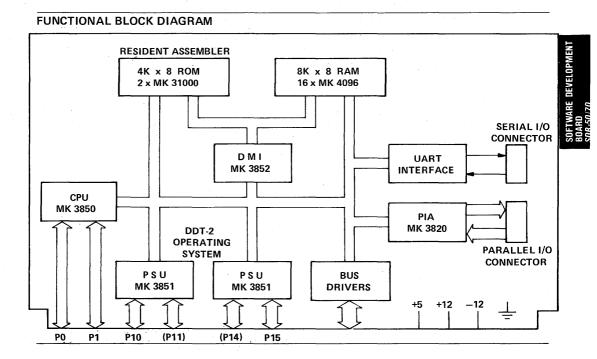

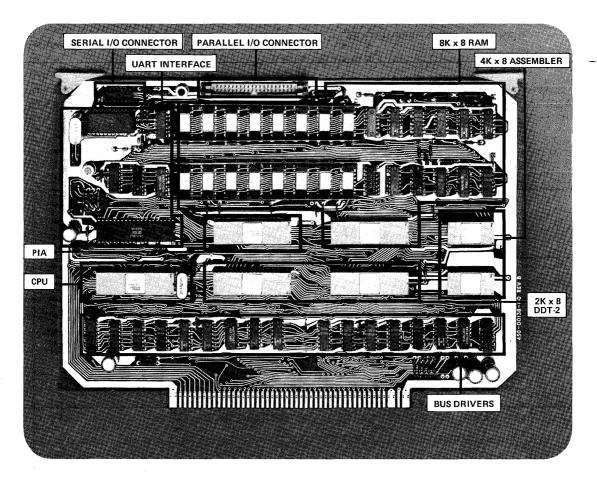

| SDB-50/70  | Software Development Board          | 3 |

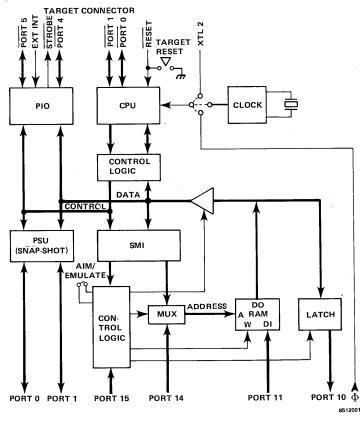

| AIM-70     | Application Interface Module        | 9 |

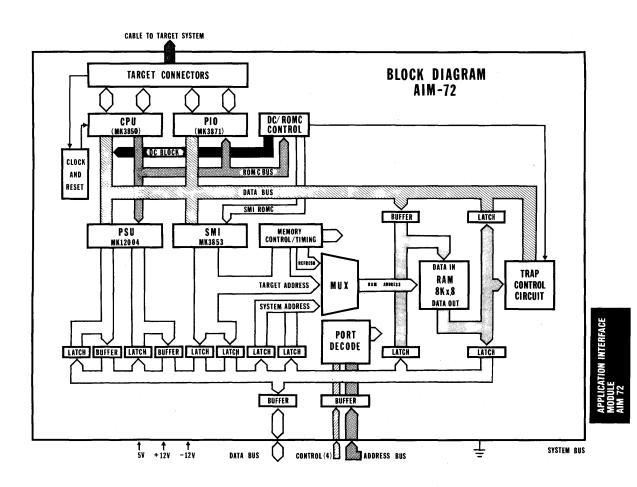

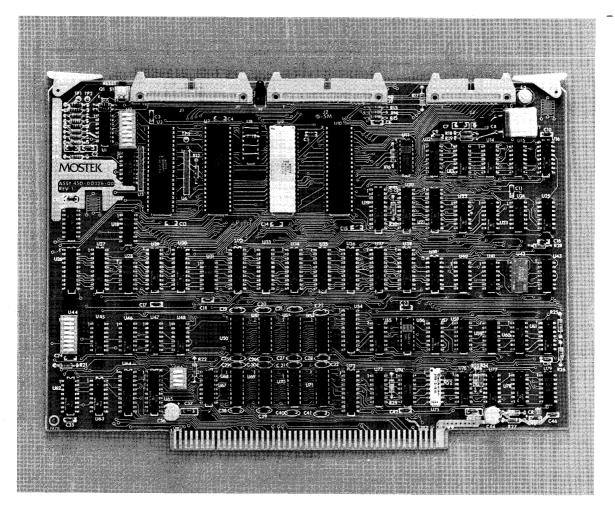

| AIM-72     | Application Interface Module        | 3 |

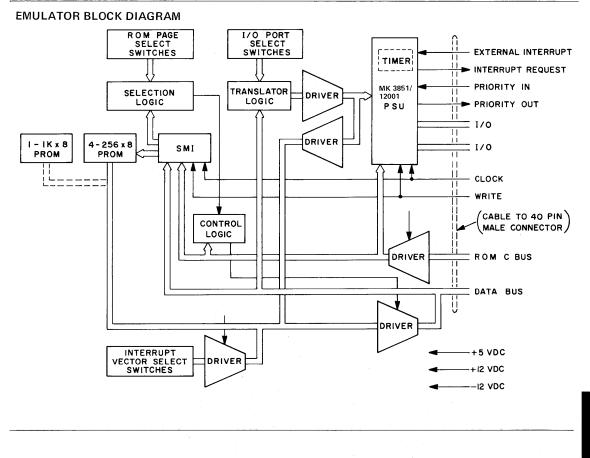

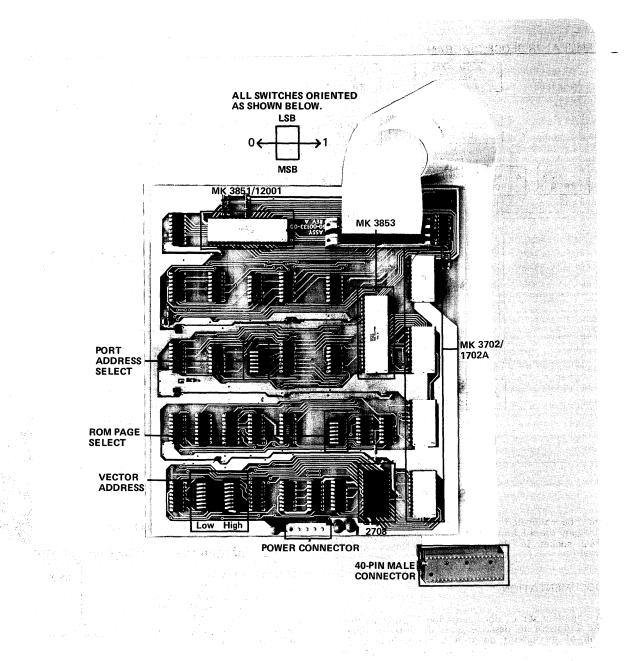

| EMU-51     | F8 PSU Emulator                     | 9 |

| EMU-70     | MK3870 Emulator                     | 3 |

| EMU-72     | 3870 Series Microcomputer Emulator  | 5 |

| XFOR-50/70 | Fortran IV Cross Assembler          | 7 |

| AID-80F    | Microcomputer Development System    | 9 |

| FZCASM     | AID 80F Cross Assembler for 3870/F8 | 7 |

|            |                                     |   |

# 3870/F8 PERIPHERAL ACCESSORIES

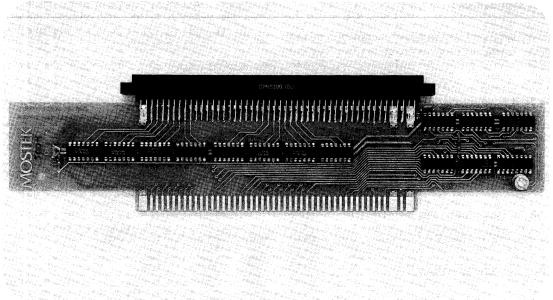

| XAID-100 | AID Station         |  |

|----------|---------------------|--|

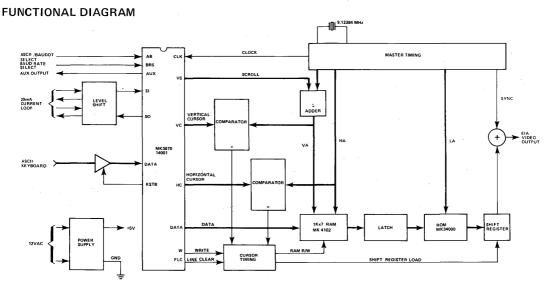

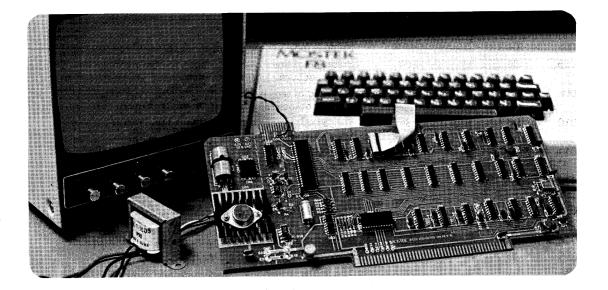

| VAB-2    | Video Adapter Board |  |

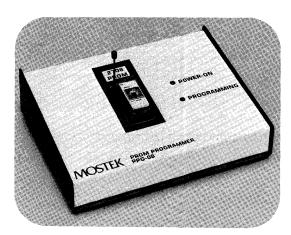

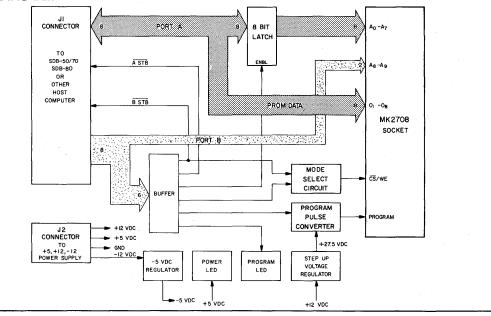

| PPG-08   | PROM Programmer     |  |

# APPLICATION NOTES

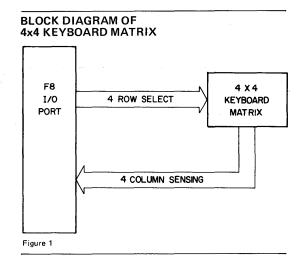

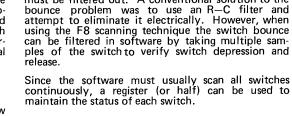

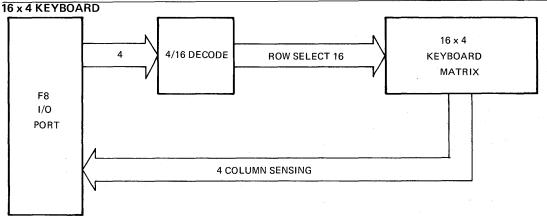

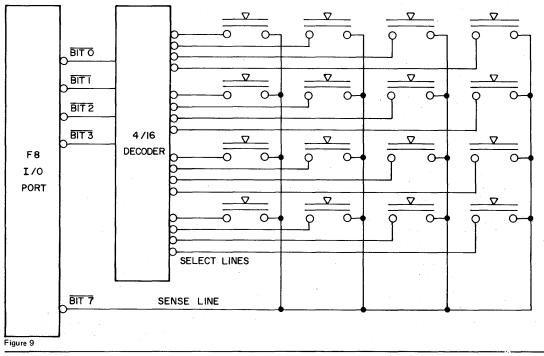

| F8 Keyboard Scanning            | <br>3 |

|---------------------------------|-------|

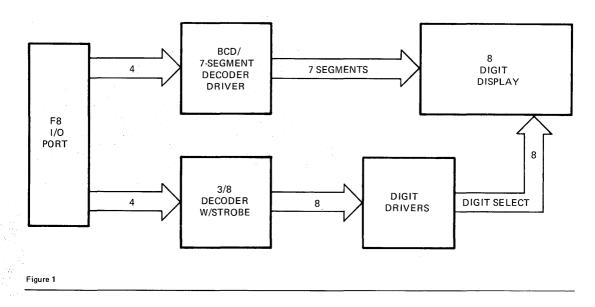

| F8 Display Multiplexing         |       |

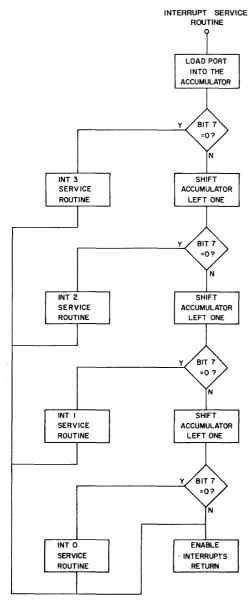

| F8 External Interrupt Expansion | <br>7 |

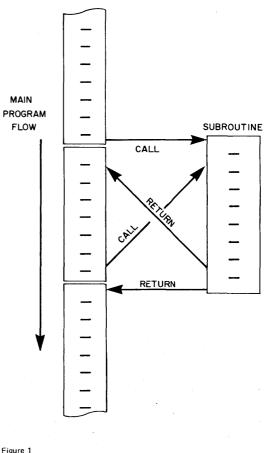

| F8 Subroutine Interrupt Nesting | <br>3 |

MICROCOMPUTER 3870/F8 DATA BOOK

# **3870 DATA SHEETS**

.

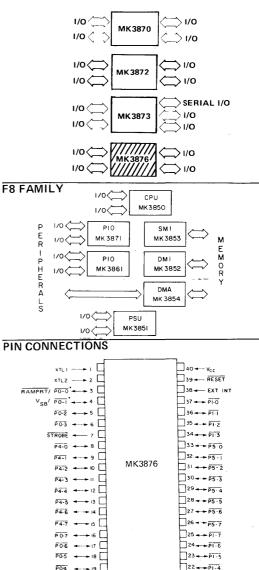

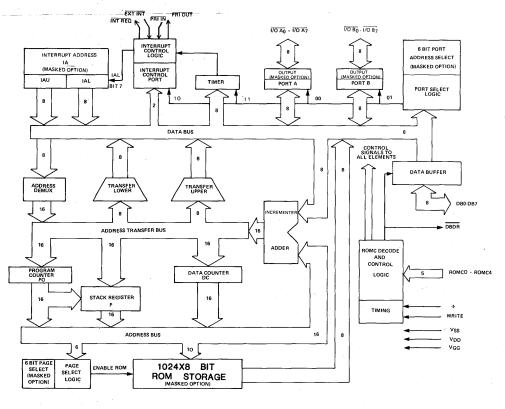

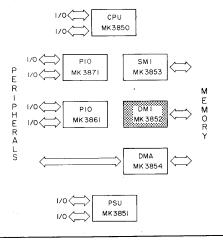

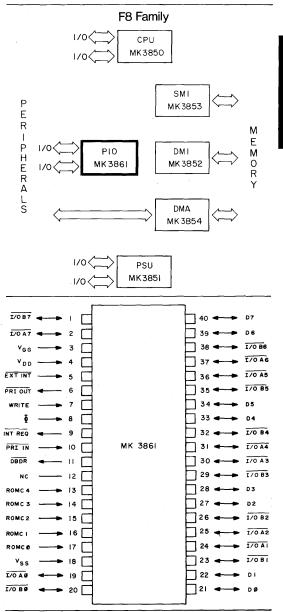

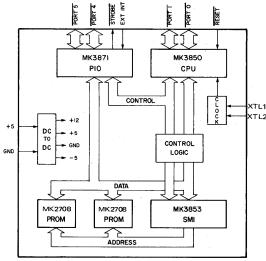

# F8 MICROCOMPUTER DEVICES

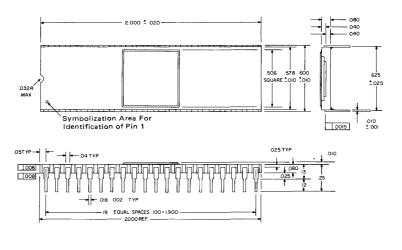

# Single-Chip Microcomputer MK 3870

# FEATURES

- Software compatible with 3870/F8 family

- 2048 X 8 mask programmable ROM

- 64 byte scratchpad RAM

- □ 32 bits (4 ports) TTL compatible I/O

- Programmable binary timer

- Interval timer mode

Pulse width measurement mode Event counter mode

- External interrupt

- Crystal, LC, RC, or external time base

- □ Low power (275 mW typ.)

- □ Single +5 volt ± 10% power supply

- D Pinout compatible with 3870 family

# GENERAL DESCRIPTION

The MK3870 is a complete 8-bit microcomputer on a single MOS integrated circuit. The 3870 can execute the F8 instruction set of more than 70 commands, allowing expansion into multi-chip configurations with software compatibility. The device features 2048 bytes of ROM, 64 bytes of scratchpad RAM, a programmable binary timer, 32 bits of I/O, and a single +5 volt power supply requirement.

Utilizing ion-implanted, N-channel silicon-gate technology and advanced circuit design techniques, the single-chip 3870 offers maximum cost effectiveness in a wide range of control and logic replacement applications.

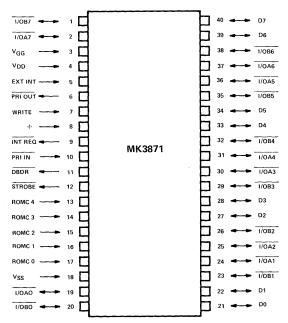

# FUNCTIONAL PIN DESCRIPTION

P0-0-P0-7, P1-0-P1-7, P4-0-P4-7, and P5-0-P5-7 are 32 lines which can be individually used as either TTL compatible inputs or as latch outputs.

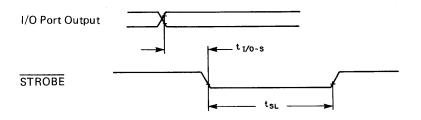

STROBE is a ready strobe associated with I/O Port 4. This pin which is normally high provides a single low pulse after valid data is present on the P4-0–P4-7 pins during an output instruction.

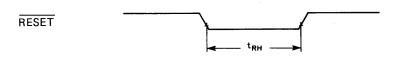

RESET may be used to externally reset the 3870. When pulled low the 3870 will reset. When then

# SINGLE CHIP 3870 MICROCOMPUTER FAMILY

| PIN NAME              | DESCRIPTION        | ТҮРЕ          |

|-----------------------|--------------------|---------------|

| P0-0 - P0-7           | I/O Port 0         | Bidirectional |

| P10-P17               | I/O Port 1         | Bidirectional |

| P4-0 - P4-7           | I/O Port 4         | Bidirectional |

| P5-0 - P5-7           | I/O Port 5         | Bidirectional |

| STROBE                | Ready Strobe       | Output        |

| EXT INT               | External Interrupt | Input         |

| RESET                 | External Reset     | Input         |

| TEST                  | Test Line          | Input         |

| XTL 1, XTL 2          | Time Base          | Input         |

| V <sub>CC</sub> , GND | Power Supply Lines | Input         |

allowed to go high the 3870 will begin program execution at program location H '000'.

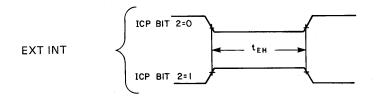

EXT INT is the external interrupt input. Its active state is software programmable. This input is also used in conjunction with the timer for pulse width measurement and event counting.

XTL 1 and XTL 2 are the time base inputs to which a crystal (1 to 4 MHz), LC network, RC network, or an external single-phase clock may be connected.

TEST is an input, used only in testing the 3870. For normal circuit functionality this pin is left unconnected or may be grounded.

VCC is the power supply input (+5V  $\pm$  10%).

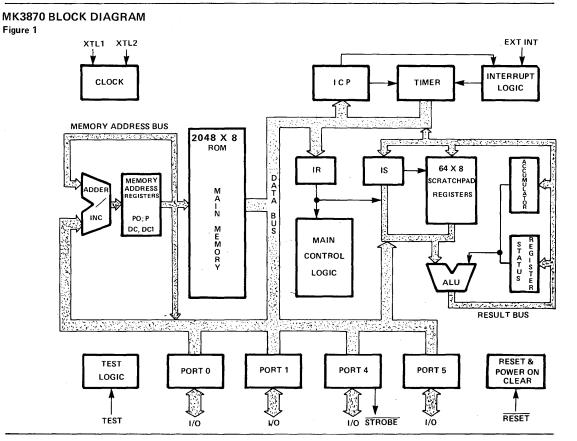

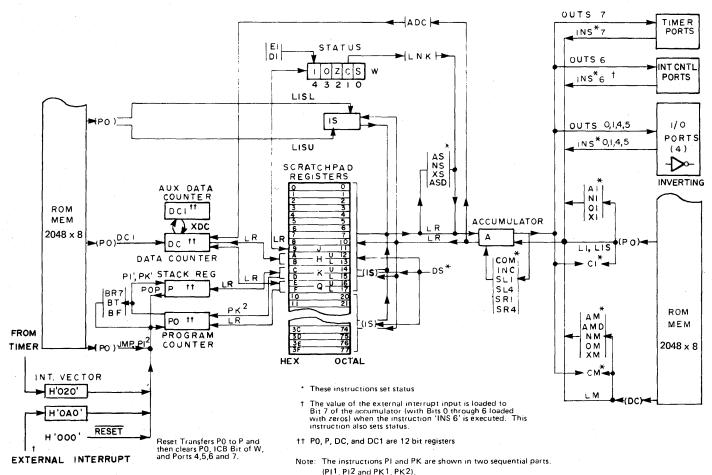

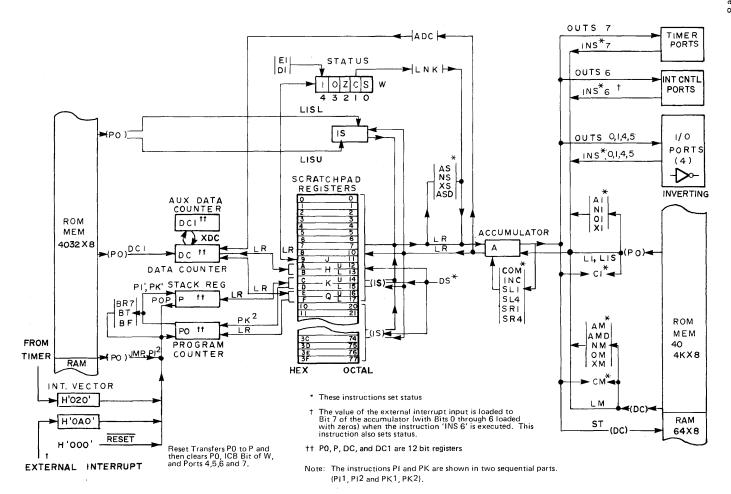

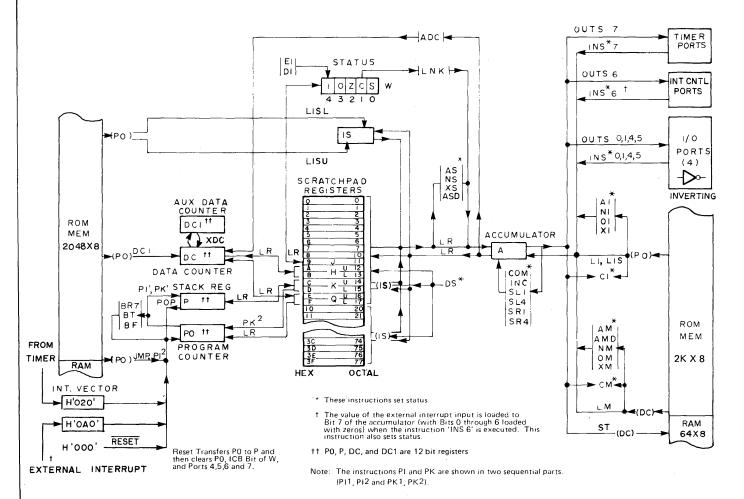

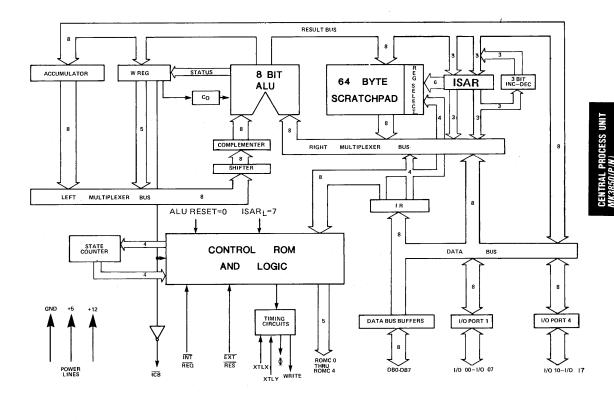

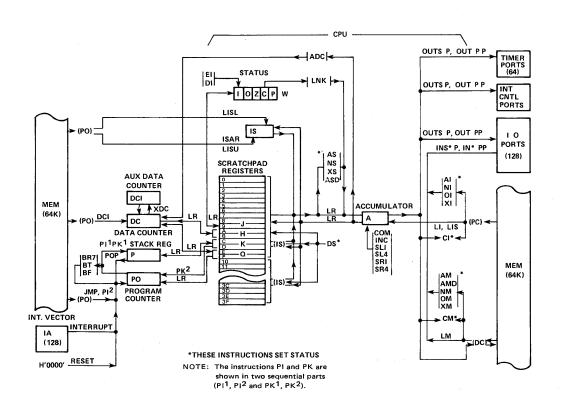

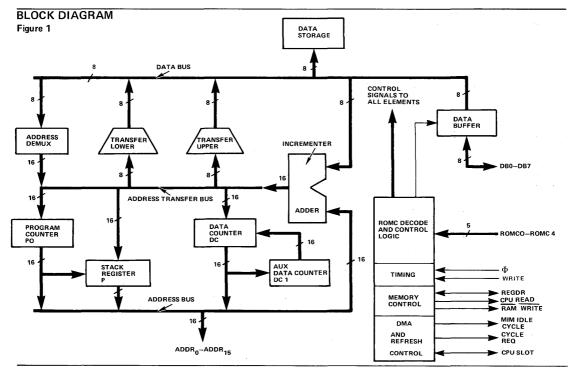

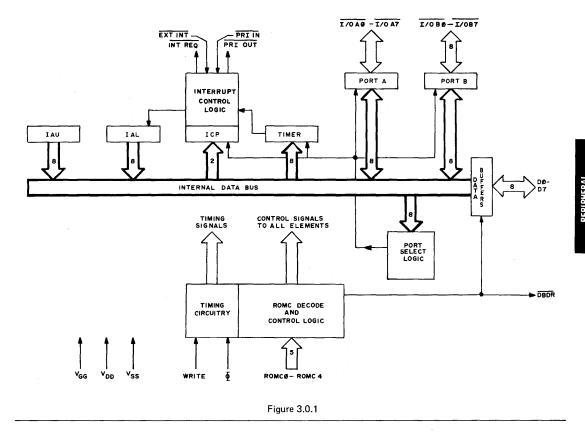

### **3870 ARCHITECTURE**

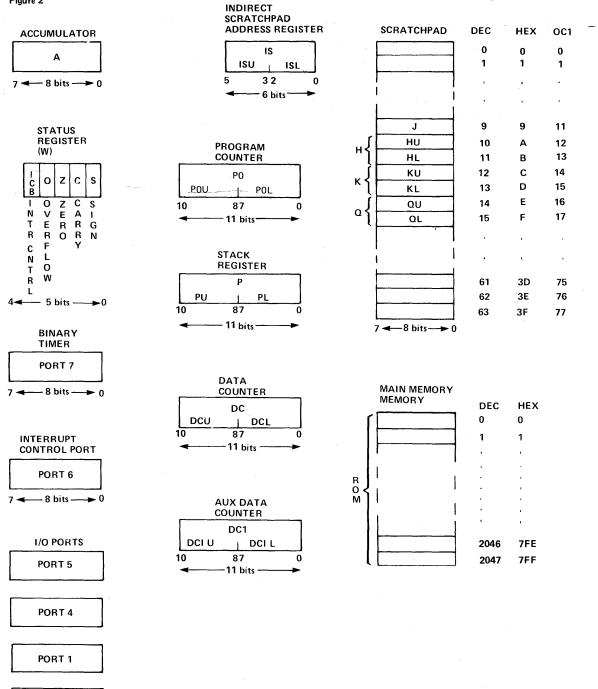

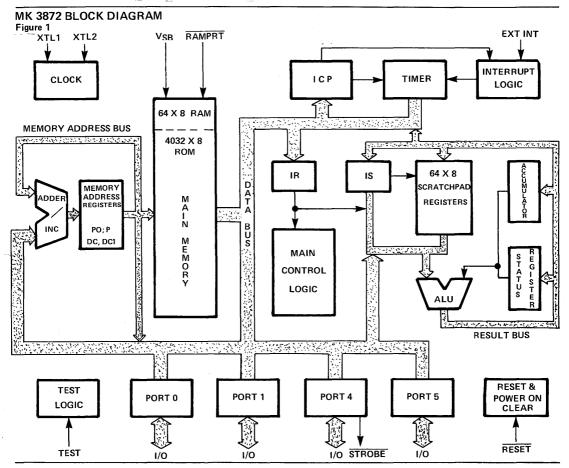

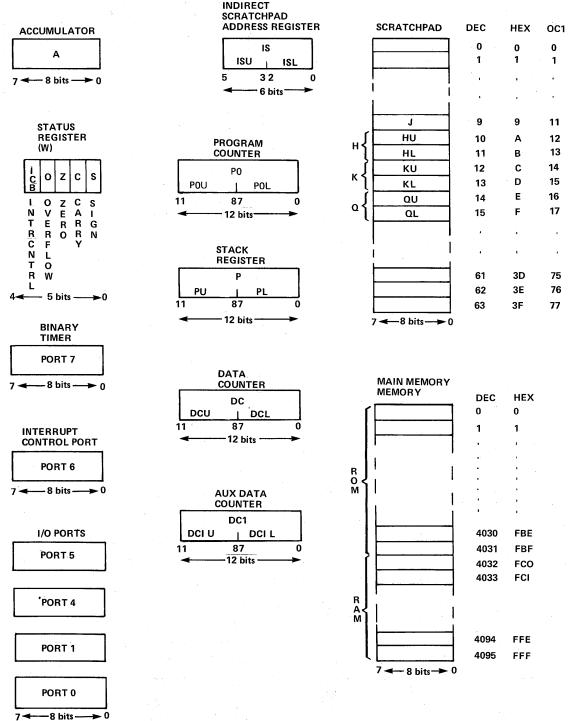

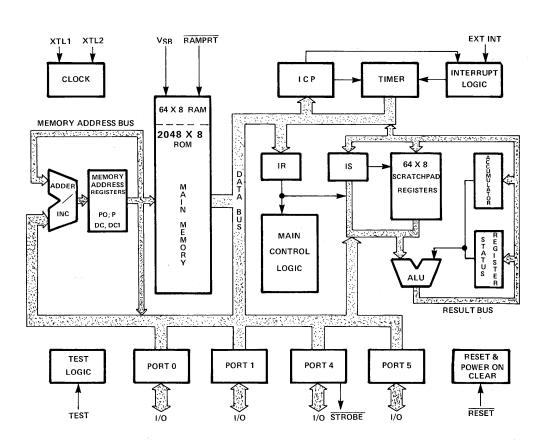

This section describes the basic functional elements of the 3870 as shown in the block diagram of Figure 1. A programming model is shown in Figure 2.

### Main Control Logic

The Instruction Register (IR) receives the operation code (OP code) of the instruction to be executed from the program ROM via the data bus. During all OP code fetches eight bits are latched into the IR. Some instructions are completely specified by the upper 4 bits of the OP code. In those instructions the lower 4 bits are an immediate register address or an immediate 4 bit operand. Once latched into the IR the main control logic decodes the instruction and provides the necessary control gating signals to all circuit elements.

### **ROM Address Registers**

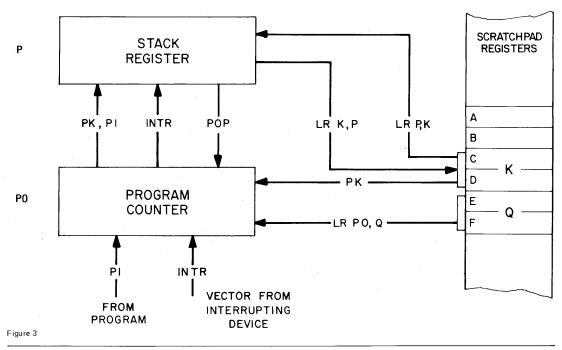

There are four 11 bit registers associated with the  $2K \times 8$  ROM. These are the Program Counter (P0), the Stack Register (P), the Data Counter (DC) and the Auxiliary Data Counter (DC1). The Program

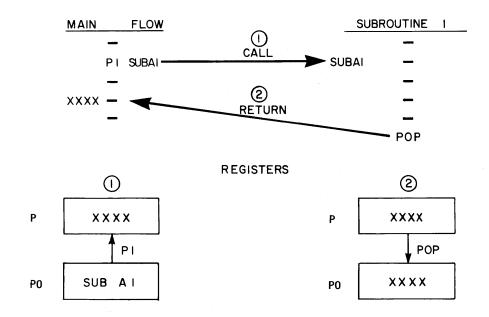

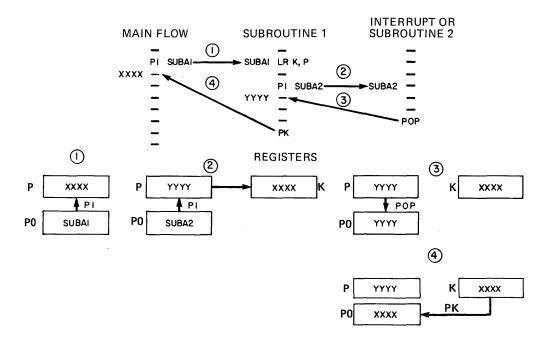

Counter is used to address instructions or immediate operands. P is used to save the contents of PO during an interrupt or subroutine call. Thus P contains the return address at which processing is to resume upon completion of the subroutine or the interrupt routine.

The Data Counter (DC) is used to address data tables. This register is auto-incrementing. Of the two data counters only DC can access the ROM. However, the XDC instruction allows DC and DC1 to be exchanged.

Associated with the address registers is an 11 bit Adder/Incrementer. This logic element is used to increment P0 or DC when required and is also used to add displacements to P0 on relative branches or to add the data bus contents to DC in the ADC (Add Data Counter) instruction.

# 2048 X 8 ROM

The microcomputer program and data constants are stored in the program ROM. When a ROM access is required, the appropriate address register (PO or DC) is gated onto the ROM address bus and the ROM output is gated onto the main data bus. The first byte in the ROM is location zero.

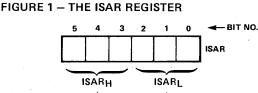

#### Scratchpad and IS

The scratchpad provides 64 8-bit registers which may be used as general purpose RAM memory. The Indirect Scratchpad Address Register (IS) is a 6 bit register used to address the 64 registers. All 64 registers may be accessed using IS. In addition the lower order 12 registers may also be directly addressed.

IS can be visualized as holding two octal digits. This division of IS is important since a number of instructions increment or decrement only the least significant 3 bits of IS when referencing scratchpad bytes via IS. This makes it easy to reference a buffer consisting of contiguous scratchpad bytes. For example, when the low order octal digit is incremented or decremented IS is incremented from octal 27 (0'27') to 0 '20) or is decremented from 0 '20' to 0 '27'. This feature of the IS is very useful in many program sequences. All six bits of IS may be loaded at one time or either half may be loaded independently.

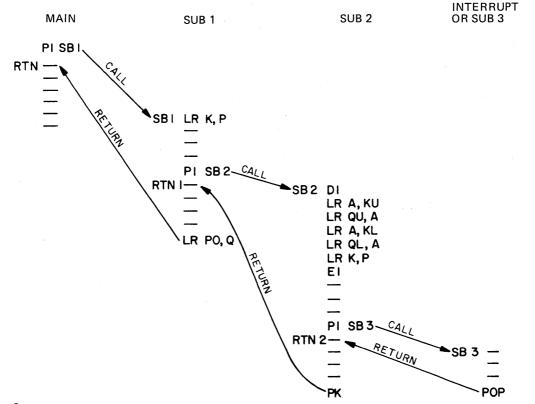

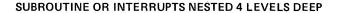

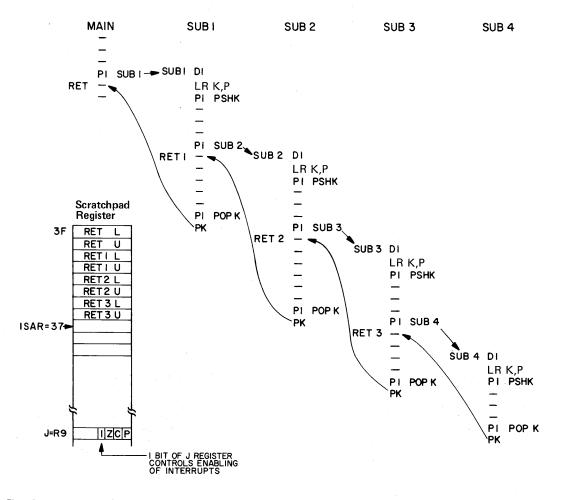

Scratchpad registers 9 through 15 (decimal) are given mnemonic names (J, H, K, and Q) because of special linkages between these registers and other registers such as the Stack Register. These special linkages facilitate the implementation of multi-level interrupts and subroutine nesting. For example, the instruction LR K,P stores the lower eight bits of the Stack Register into register 13 (K lower or KL) and stores the upper three bits of P into register 12 (K upper or KU).

# Arithmetic and Logic Unit (ALU)

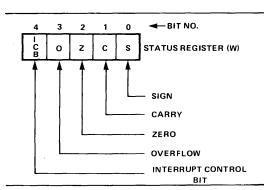

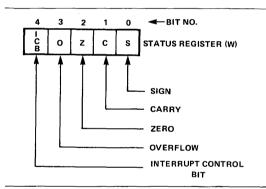

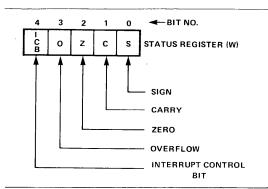

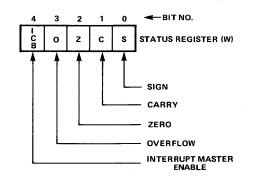

After receiving commands from the main control logic, the ALU performs the required arithmetic or logic operations (using the data presented on the two input busses) and provides the result on the result bus. The arithmetic operations that can be performed in the ALU are binary add, decimal adjust, add with carry, decrement, and increment. The logic operations that can be performed are AND, OR, EXCLUSIVE OR, 1's complement, shift right, and shift left. Besides providing the result on the result bus, the ALU also provides four signals representing the status of the result. These signals, stored in the Status Register (W), represent CARRY, OVERFLOW, SIGN, and ZERO condition of the result of the operation.

# Accumulator(A)

The Accumulator (A) is the principal register for data manipulation within the 3870. The A serves as one input to the ALU for arithmetic or logical operations. The result of ALU operations are stored in the A.

Summary of Status Bits

| OVERFLOW = | CARRY 7 CARRY 6                                                                                                                                                                                  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZERO =     | $\frac{\overline{ALU_7} \wedge \overline{ALU_6} \wedge \overline{ALU_5} \wedge \overline{ALU_4} \wedge \overline{ALU_3} \wedge \overline{ALU_2} \wedge \overline{ALU_1} \wedge \overline{ALU_0}$ |

| CARRY =    | CARRY7                                                                                                                                                                                           |

| SIGN =     | ALU7                                                                                                                                                                                             |

# 3870 PROGRAMMABLE REGISTERS, PORTS AND MEMORY MAP

Figure 2

7-

PORT 0

-8 bits ----- 0

# SINGLE CHIP $\mu$ C-2K rom *ink3870(p/n)*

# The Status Register(W)

The Status Register (also called the W register) holds five status flags as follows:

# Interrupt Control Bit (ICB)

The ICB may be used to allow or disallow interrupts in the 3870. This bit is not the same as the two interrupt enable bits in the Interrupt Control Port (ICP). If the ICB is set and the 3870 interrupt logic communicates an interrupt request to the CPU section, the interrupt will be acknowledged and processed upon completion of the first non-privileged instruction. If the ICB is cleared an interrupt request will not be acknowledged or processed until the ICB is set.

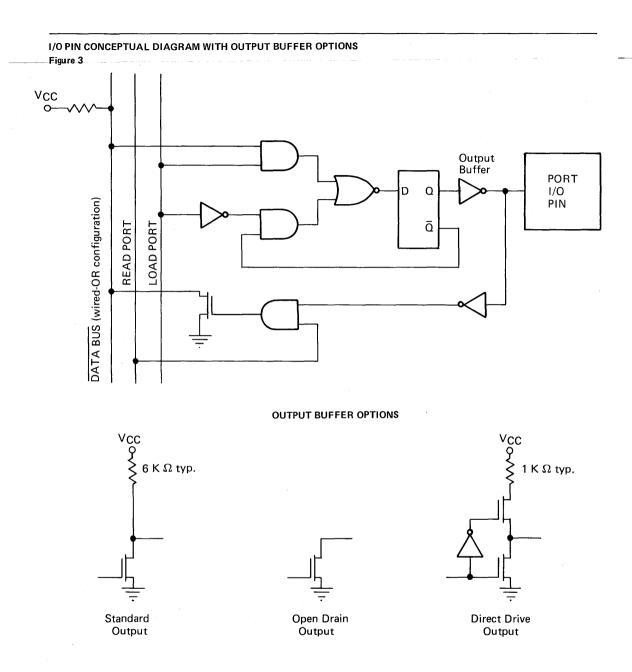

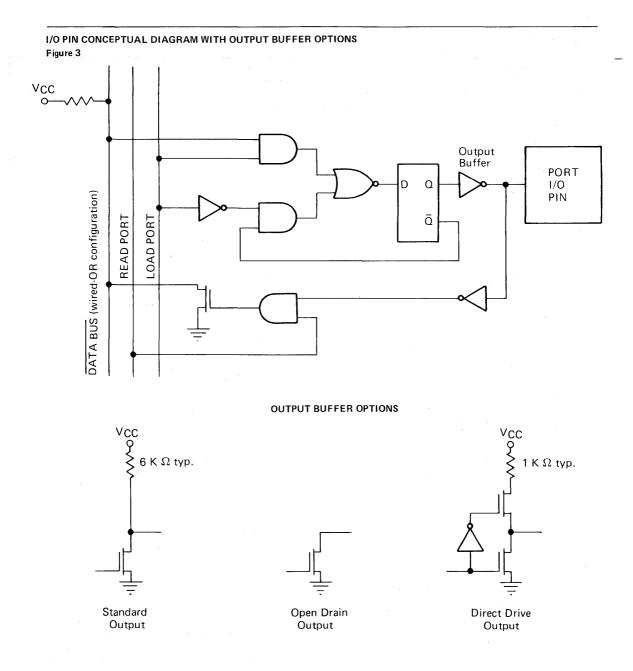

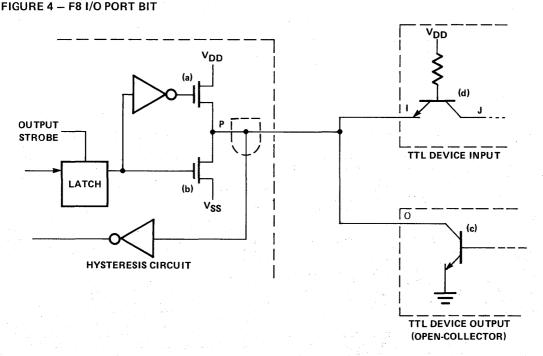

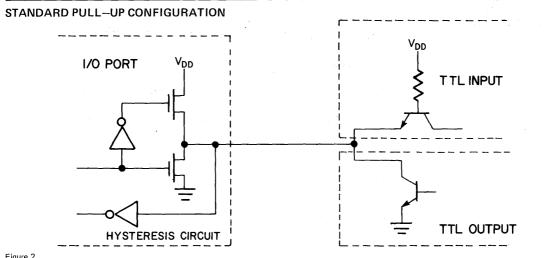

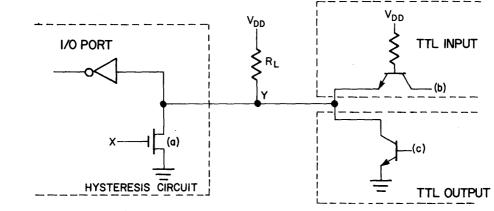

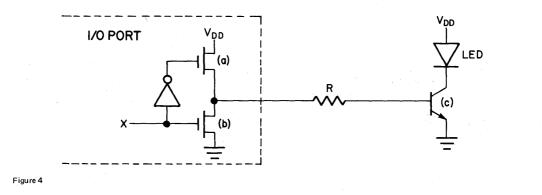

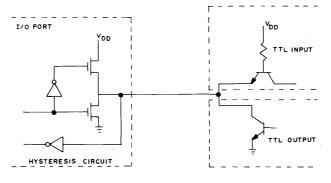

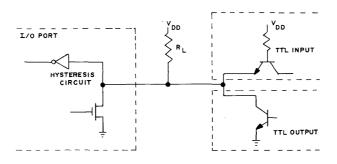

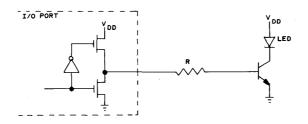

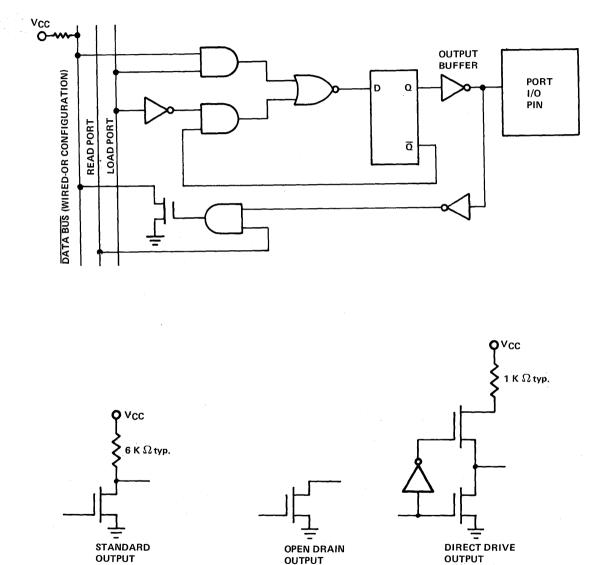

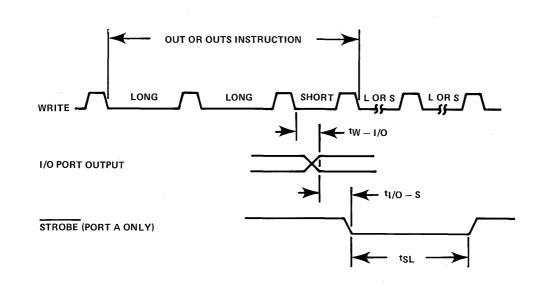

# I/O Ports

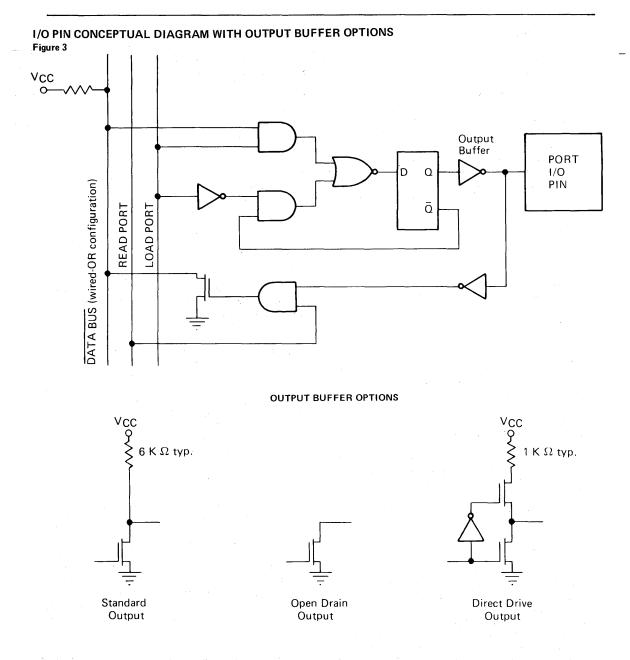

The 3870 provides four complete bidirectional Input/Output ports. These are ports 0, 1, 4, and 5. In addition, the Interrupt Control Port is addressed as port 6 and the binary timer is addressed as port 7. An output instruction (OUT or OUTS) causes the contents of A to be latched into the addressed port. An input instruction (IN or INS) transfers the contents of the port to A (port 6 is an exception which is described later). The schematic of an I/O pin and available output drive options are shown in Figure 3.

An output ready strobe is associated with port 4. This flag may be used to signal a peripheral device that the 3870 has just completed an output of new data to port 4. The strobe provides a single low pulse shortly after the output operation is completely finished, so either edge may be used to signal the peripheral. STROBE may also be used as an input strobe simply by doing a dummy output of H '00' strobe to port 4 after completing the input operation.

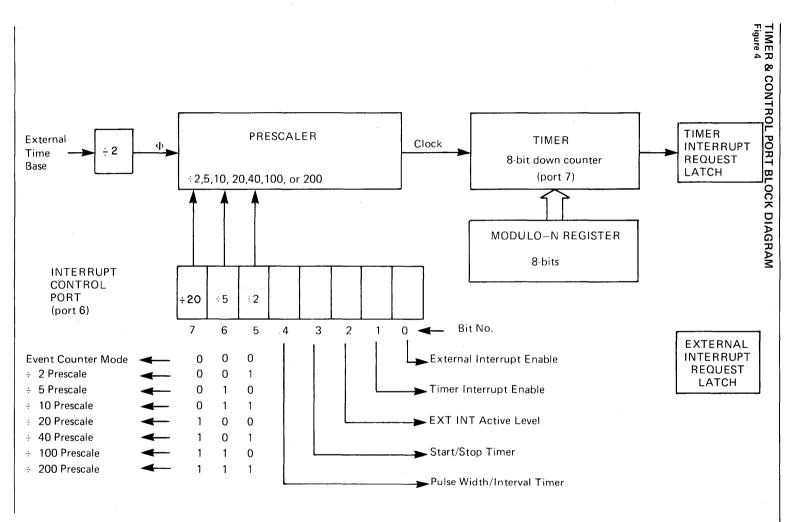

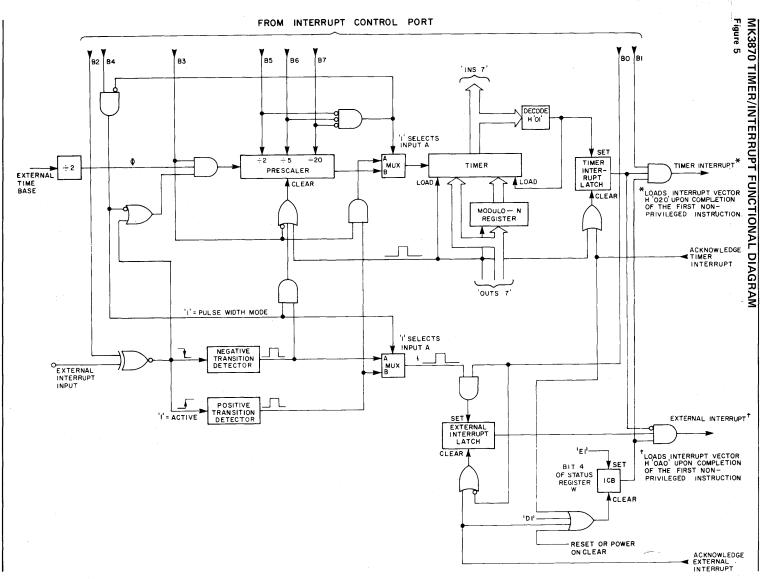

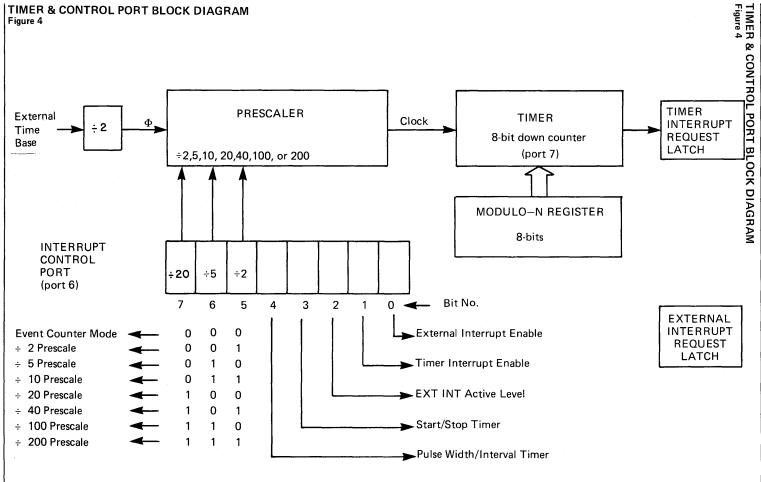

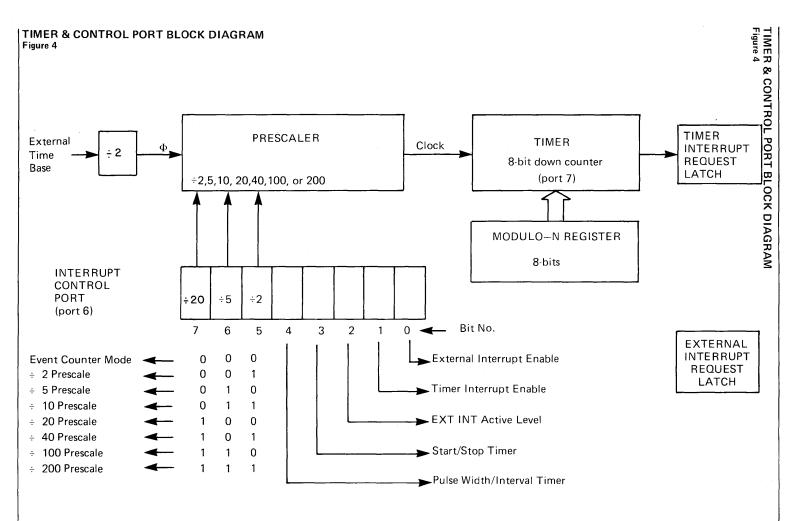

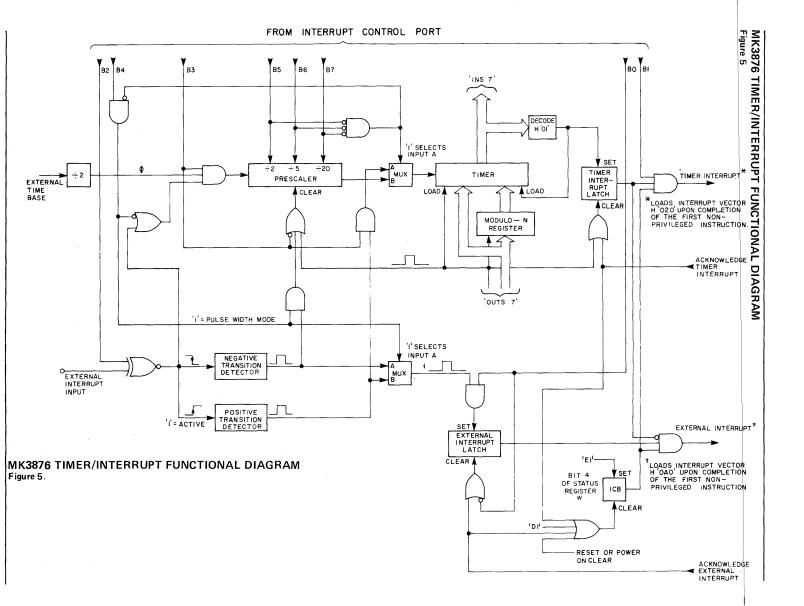

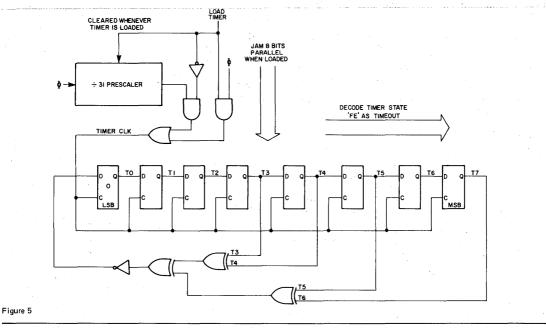

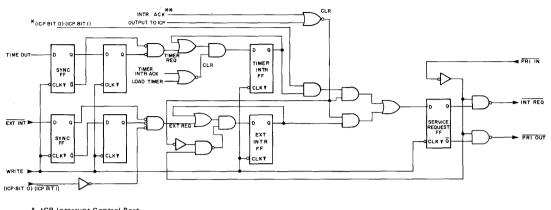

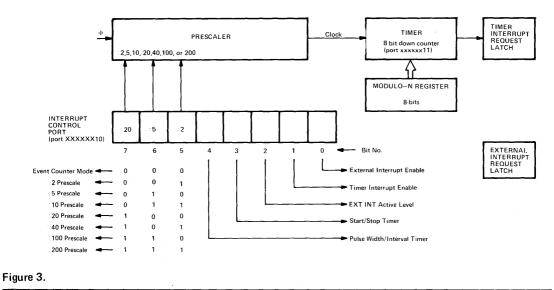

# Timer and Interrupt Control Port

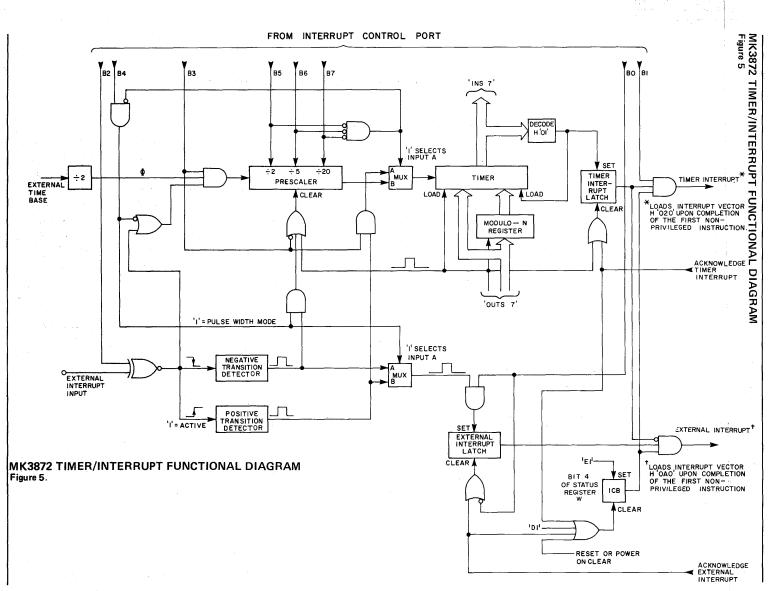

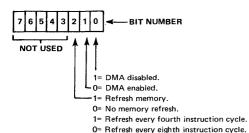

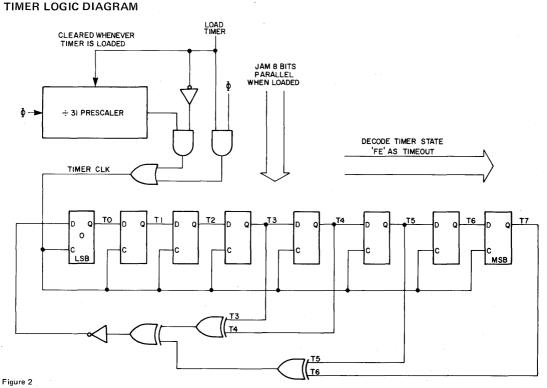

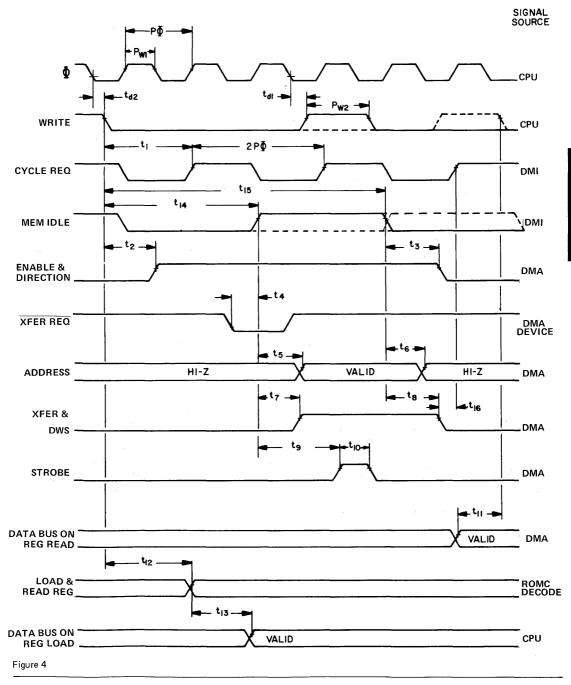

The Timer is an 8-bit binary down counter which is software programmable to operate in one of three modes: the Interval Timer Mode, the Pulse Width Measurement Mode, or the Event Counter Mode. As shown in Figure 4, associated with the Timer are an 8-bit register called the Interrupt Control Port, a programmable prescaler, and an 8-bit modulo-N register. A functional logic diagram is shown in Figure 5.

The desired timer mode, prescale value, starting and stopping the timer, active level of the EXT INT pin, and local enabling or disabling of interrupts are selected by outputting the proper bit configuration from the Accumulator to the Interrupt Control Port (port 6) with an OUT or OUTS instruction. Bits within the Interrupt Control Port are defined as follows:

# **Interrupt Control Port (Port 6)**

Bit 0 - External Interrupt Enable Bit 1 - Timer Interrupt Enable Bit 2 - EXT INT Active Level Bit 3 - Start/Stop Timer Bit 4 - Pulse Width/Interval Timer Bit 5 - ÷ 2 Prescale Bit 6 - ÷ 5 Prescale Bit 7 - ÷ 20 Prescale

A special situation exists when reading the Interrupt Control Port (with an IN or INS instruction). The Accumulator is not loaded with the content of the ICP; instead, Accumulator bits 0 through 6 are loaded with 0's while bit 7 is loaded with the logic level being applied to the EXT INT pin, thus allowing the status of EXT INT to be determined without the necessity of servicing an external interrupt request. When reading the Interrupt Control Port (Port 6) bit 7 of the Accumulator is loaded with the actual logic level being applied to the EXT INT pin, regardless of the status of ICP bit 2 (the EXT INT Active Level bit); that is, if EXT INT is at +5V bit 7 of the Accumulator is set to a logic 1, but if EXT INT is at GND then Accumulator bit 7 is reset to logic 0. This capability is useful in establishing a high speed polled handshake procedure or for using EXT INT as an extra input pin if external interrupts are not required and the Timer is used only in the Interval Timer Mode. However, if it is desirable to read the contents of the ICP then one of the 64 scratchpad registers or one byte of RAM may be used to save a copy of whatever is written to the ICP.

The rate at which the timer is clocked in the Interval Timer Mode is determined by the frequency of an internal  $\Phi$  clock and by the division value selected for the prescaler. (The internal  $\Phi$  clock operates at one-half the external time base frequency). If ICP bit 5 is set and bits 6 and 7 are cleared, the prescaler divides  $\Phi$  by 2. Likewise, if bit 6 or 7 is individually set the prescaler divides  $\Phi$  by 5 or 20 respectively. Combinations of bits 5, 6 and 7 are set while 6 is cleared the prescaler will divide by 40. Thus possible prescaler values are  $\pm 2$ ,  $\pm 5$ ,  $\pm 10$ ,  $\pm 20$ ,  $\pm 40$ ,  $\pm 100$ , and  $\pm 200$ .

Any of three conditions will cause the prescaler to be reset: whenever the timer is stopped by clearing ICP bit 3, execution of an output instruction to Port 7, (the timer is assigned port address 7), or on the trailing edge transition of the EXT INT pin when in the Pulse Width Measurement Mode. These last two conditions are explained in more detail below.

An OUT or OUTS instruction to Port 7 will load the content of the Accumulator to both the Timer and the 8-bit modulo-N register, reset the prescaler, and

Ports 0 and 1 are Standard Output type only.

Ports 4 and 5 may both be any of the three output options (programmable bit by bit).

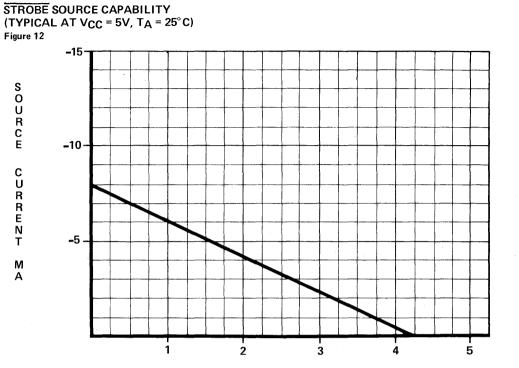

The STROBE output is always configured similar to a Direct Drive Output except that it is capable of driving 3 TTL loads.

**RESET** and EXT INT may have standard  $6K\Omega$  (typical) pull-up or may have no pull-up. These two inputs have Schmidt trigger inputs with a minimum of 0.2 volts of hysteresis.

8

Note: See Figure 5 for a more detailed functional diagram.

clear any previously stored timer interrupt request. As previously noted, the Timer is an 8-bit down counter which is clocked by the prescaler in the Interval Timer Mode and in the Pulse Width Measurement Mode. The prescaler is not used in the Event Counter Mode. The Modulo-N register is a buffer whose function is to save the value which was most recently outputted to Port 7. The modulo-N register is used in all three timer modes.

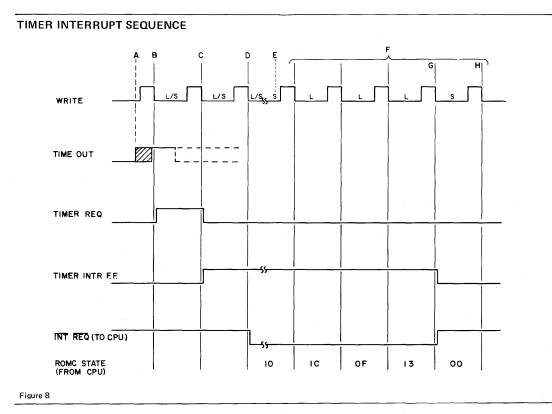

## Interval Timer Mode

When ICP bit 4 is cleared (logic 0) and at least one prescale bit is set the Timer operates in the Interval Timer Mode. When bit 3 of the ICP is set the Timer will start counting down from the modulo-N value. After counting down to H'01', the Timer returns to the modulo-N value at the next count. On the transition from H'01' to H 'N' the Timer sets a timer interrupt request latch. Note that the interrupt request latch is set by the transition to H 'N' and not be the presence of H 'N' in the Timer, thus allowing a full 256 counts if the modulo-N register is preset to H '00'. If bit 1 of the ICP is set, the interrupt request is passed on to the CPU section of the 3870. However, if bit 1 of the ICP is a logic 0 the interrupt request is not passed on to the CPU section but the interrupt request latch remains set. If ICP bit 1 is subsequently set, the interrupt request will then be passed on to the CPU section. (Recall from the discussion of the Status Register's Interrupt Control Bit that the interrupt request will be acknowledged by the CPU section only if ICB is set). Only two events can reset the timer interrupt request latch; when the timer interrupt request latch is acknowledged by the CPU section, or when a new load of the modulo-N register is performed.

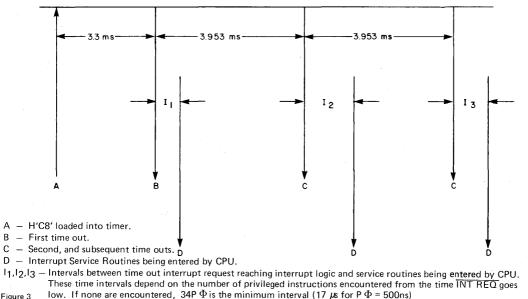

Consider an example in which the modulo-N register is loaded with H '64' (decimal 100). The timer interrupt request latch will be set at the 100th count following the timer start and the timer interrupt request latch will repeatedly be set on precise 100 count intervals. If the prescaler is set at ÷40 the timer interrupt request latch will be set every 4000  $\Phi$  clock periods. For a 2MHz  $\Phi$  clock (4MHz time base frequency) this will produce 2 millisecond intervals.

The range of possible intervals is from 2 to 51,200  $\Phi$  clock periods (1µs to 25.6ms for a 2MHz $\Phi$  clock). However, approximately 50  $\Phi$  periods is a practical minimum because the time between setting the interrupt request latch and the execution of the first instruction of the interrupt service routine is at least 29  $\Phi$  periods (the response time is dependent upon how many privileged instructions are encountered when the request occurs); 29 is based on the timer interrupt occuring at the beginning of a non-priviledged short instruction. To establish time intervals greater than 51,200  $\Phi$  clock periods is a simple matter of using the timer interrupt service routine to count the number of interrupts, saving the result in one or more of the scratchpad registers until the desired interval is achieved. With this technique virtually any time interval, or several time intervals, may be generated.

The Timer may be read at any time and in any mode using an input instruction (IN 7 or INS 7) and may take place "on the fly" without interfering with normal timer operation. Also, the Timer may be stopped at any time by clearing bit 3 of the ICP. The Timer will hold its current contents indefinitely and will resume counting when bit 3 is again set. Recall however that the prescaler is reset whenever the Timer is stopped; thus a series of starting and stopping will result in a cumulative truncation error.

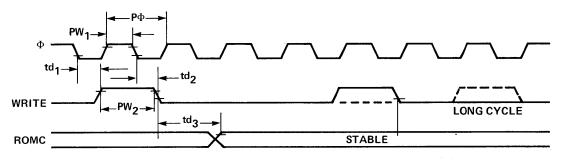

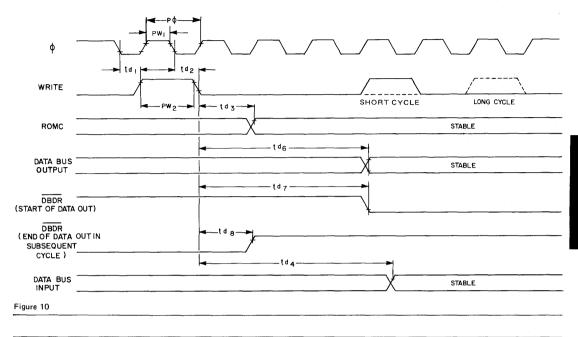

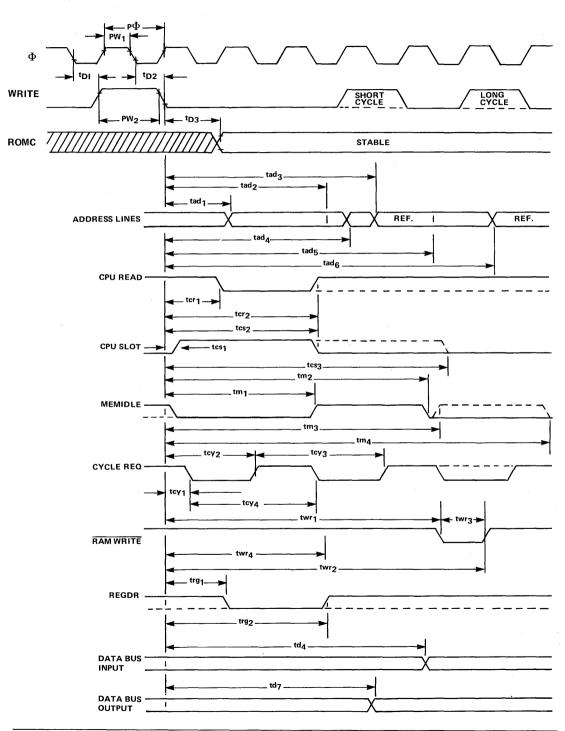

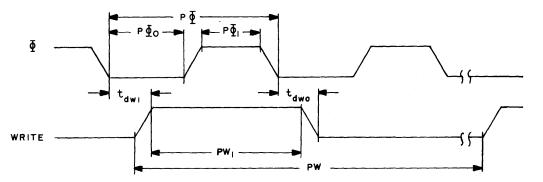

A summary of other timer errors is given in the timing section of this specification. For a free running timer in the Interval Timer Mode the time interval between any two interrupt requests may be in error by  $\pm$  6  $\Phi$  clock periods although the cumulative error over many intervals is zero. The prescaler and Timer generate precise intervals for setting the timer interrupt request latch but the time out may occur at any time within a machine cycle. (There are two types of machine cycles; short cycles which consist of 4  $\Phi$  clock periods and long cycles which consist of 6  $\Phi$  clock periods. In the multi-chip F8 family there is a signal called the WRITE clock which corresponds to a machine cycle). Interrupt requests are synchronized with the internal WRITE clock thus giving rise to the possible  $\pm$  6  $\Phi$  error. Additional errors may arise due to the interrupt request occuring while a privileged instruction or multicycle instruction is being executed. Nevertheless, for most applications all of the above errors are negligible, especially if the desired time interval is greater than 1 ms.

# Pulse Width Measurement Mode

When ICP bit 4 is set (logic 1) and at least one prescale bit is set the Timer operates in the Pulse Width Measurement Mode. This mode is used for accurately measuring the duration of a pulse applied to the EXT INT pin. The Timer is stopped and the prescaler is reset whenever EXT INT is at its inactive level. The active level of EXT INT is defined by ICP bit 2; if cleared, EXT INT is active low; if set, EXT INT is active high. If ICP bit 3 is set, the prescaler and Timer will start counting when EXT INT transitions to the active level. When EXT INT returns to the inactive level the Timer then stops, the prescaler resets, and if ICP bit 0 is set an external interrupt request latch is set. (Unlike timer interrupts, external interrupts are not latched if the ICP Interrupt Enable bit is not set).

As in the Interval Timer Mode, the Timer may be read at any time, may be stopped at any time by clearing ICP bit 3, the prescaler and ICP bit 1 function as previously described, and the Timer still functions as an 8-bit binary down counter with the timer interrupt request latch being set on the Timer's transition from H '01' to H 'N'. Note that the EXT INT pin has nothing to do with loading the Timer; its action is that of automatically starting and stopping the Timer and of generating external interrupts. Pulse widths longer than the prescale value times the modulo-N value are easily measured by using the timer interrupts in one or more scratchpad registers.

As for accuracy, the actual pulse duration is typically slightly longer than the measured value because the status of the prescaler is not readable and is reset when the Timer is stopped. Thus for maximum accuracy it is advisable to use a small division setting for the prescaler.

### Event Counter Mode

When ICP bit 4 is cleared and all prescale bits (ICP bits 5, 6, and 7) are cleared the Timer operates in the Event Counter Mode. This mode is used for counting pulses applied to the EXT INT pin. If ICP bit 3 is set the Timer will decrement on each transition from the inactive level to the active level of the EXT INT pin. The prescaler is not used in this mode; but as in the other two timer modes, the Timer may be read at any time, may be stopped at any time by clearing ICP bit 3, ICP bit 1 functions previously described, and the timer interrupt request latch is set on the Timer's transition from H '01' to H 'N'.

Normally ICP bit 0 should be kept cleared in the Event Counter Mode; otherwise, external interrupts will be generated on the transition from the inactive level to the active level of the EXT INT pin.

For the Event Counter Mode the minimum pulse width required on EXT INT is 2  $\Phi$  clock periods and the minimum inactive time is 2  $\Phi$  clock periods; therefore, the maximum repetition rate is 500 KHz.

# **Timer Emulation**

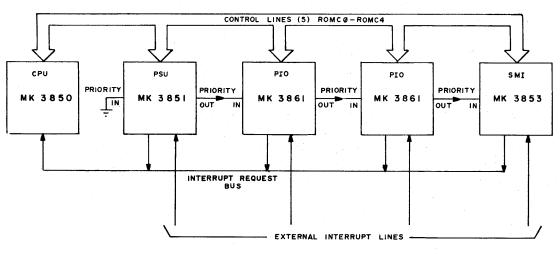

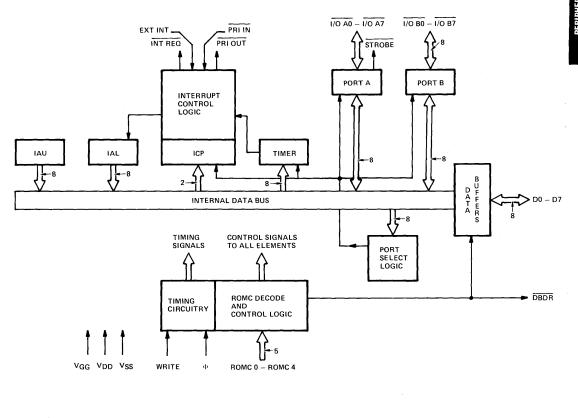

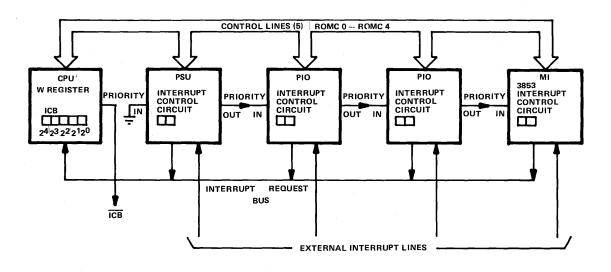

For total software compatibility when expanding into a multi-chip configuration the MK3871 Peripheral Input/Output circuit should be used rather than the older MK3861 PIO. The MK3871 has the same improved Timer (binary count, readable, and three modes of operation rather than one) and ready strobe output as are on the MK3870.

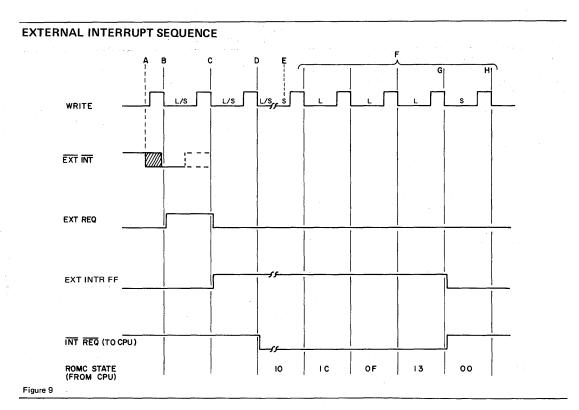

### External Interrupts

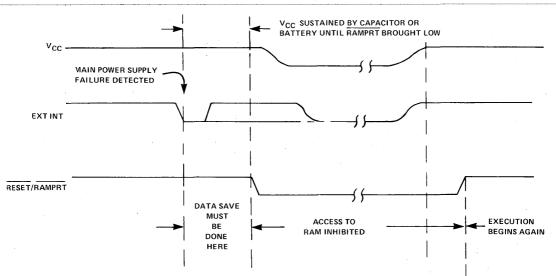

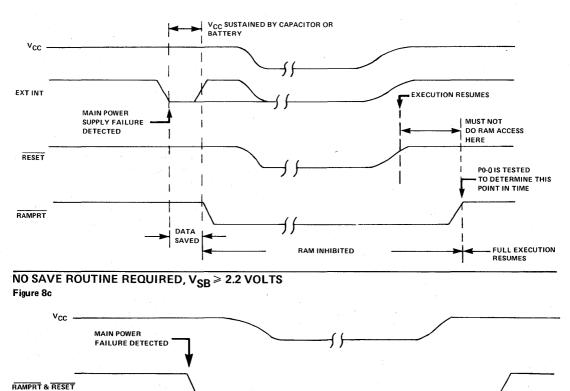

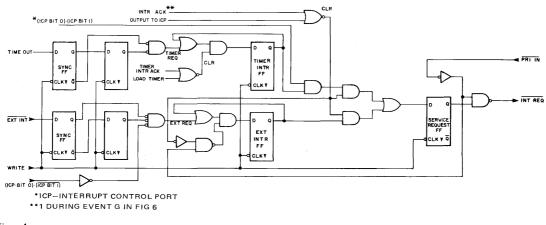

When the timer is in the Interval Timer Mode the

EXT INT pin is available for non-timer related interrupts. If ICP bit 0 is set an external interrupt request latch is set when there is a transition from the inactive level to the active level of EXT INT. (EXT INT is an edge-triggered input). The interrupt request is latched until either acknowledged by the CPU section or until ICP bit 0 is cleared (unlike timer interrupt requests which remain latched even when ICP bit 1 is cleared). External interrupts are handled in the same fashion when the Timer is in the Pulse Width Measurement Mode or in the Event Counter Mode, except that only in the Pulse Width Measurement Mode the external interrupt request latch is set on the trailing edge of EXT INT; that is, on the transition from the active level to the inactive level.

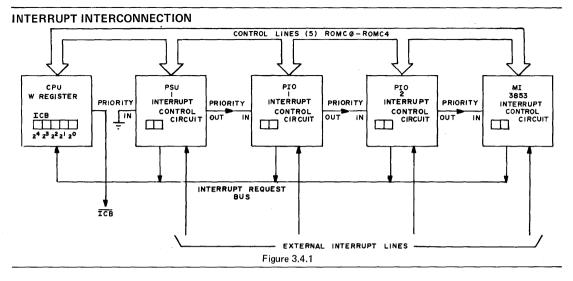

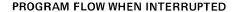

### Interrupt Handling

When either a timer or an external interrupt request is communicated to the CPU section of the 3870, it will be acknowledged and processed at the completion of the first non-privileged instruction if the Interrupt Control Bit of the Status Register is set. If the Interrupt Control Bit is not set, the interrupt request will continue until either the Interrupt Control Bit is set and the CPU section acknowledges the interrupt or until the interrupt request is cleared as previously described.

If there is both a timer interrupt request and an external interrupt request when the CPU section starts to process the requests, the timer interrupt is handled first.

When an interrupt is allowed the CPU section will request that the interrupting element pass its interrupt vector address to the Program Counter via the data bus. The vector address for a timer interrupt is H '020'. The vector address for external interrupts is H '0A0'. After the vector address is passed to the Program Counter, the CPU section sends an acknowledge signal to the appropriate interrupt request latch which clears that latch. The exection of the interrupt service routine will then commence. The return address of the original program is automatically saved in the Stack Register, P.

The Interrupt Control Bit of W (Status Register) is automatically reset when an interrupt request is acknowledged. It is then the programmer's responsibility to determine when ICB will again be set (by executing an EI instruction). This action prevents an interrupt service routine from being interrupted unless the programmer so desires.

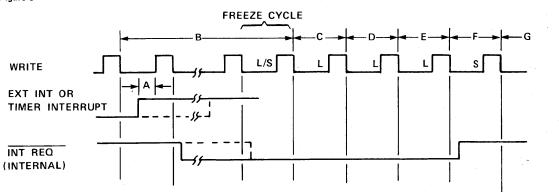

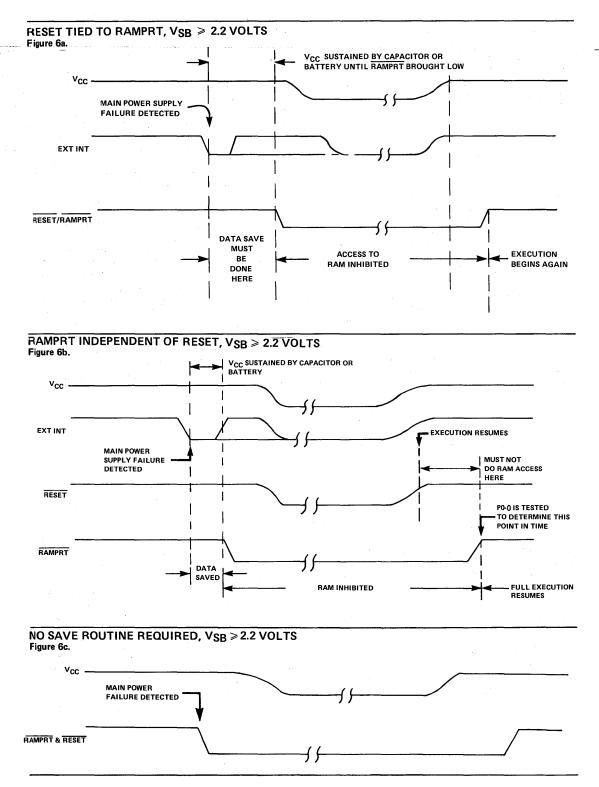

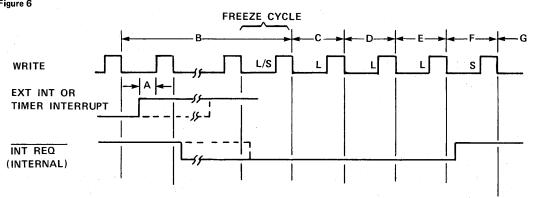

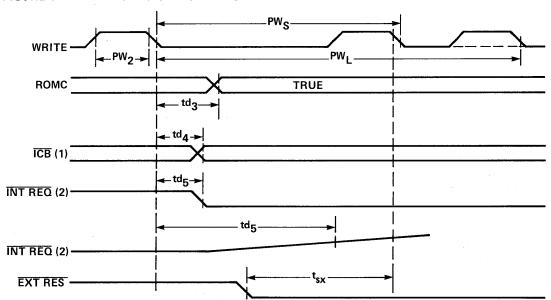

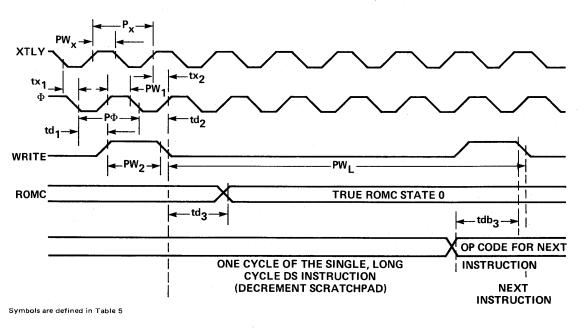

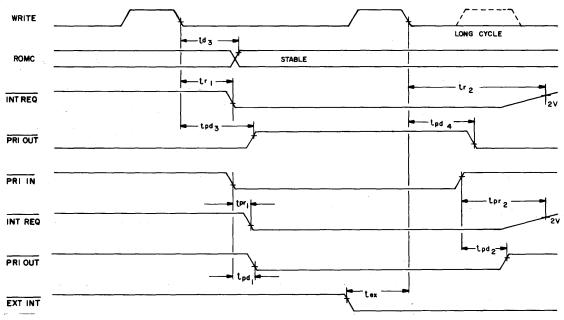

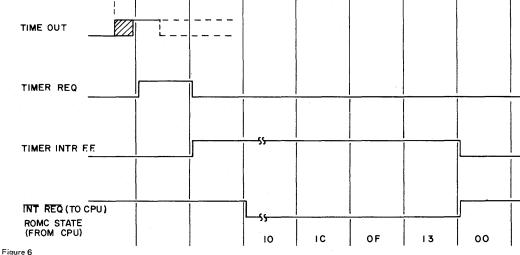

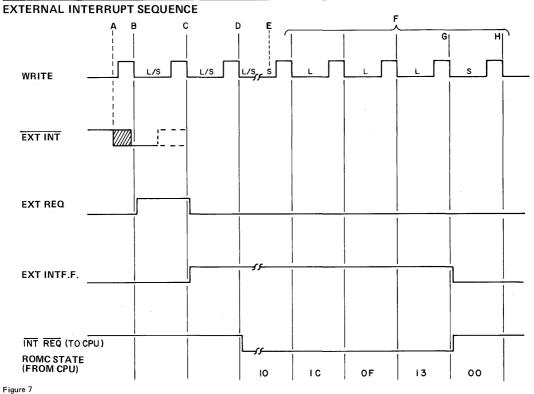

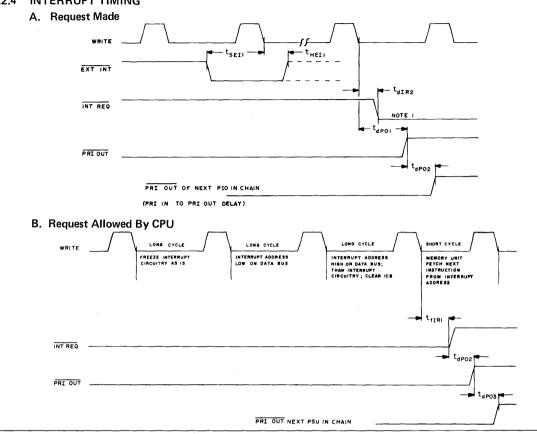

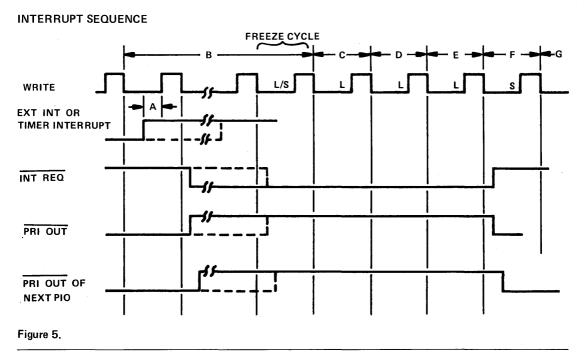

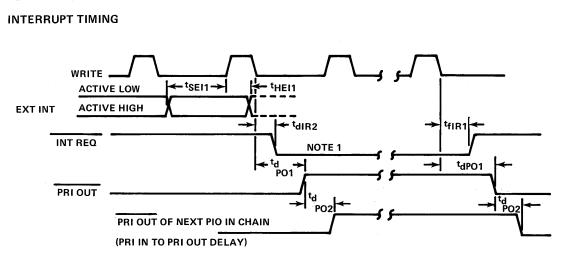

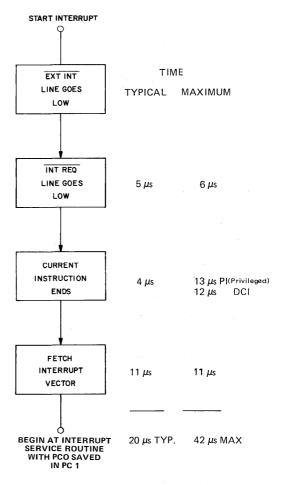

Figure 6 details the interrupt sequence which occurs whether the interrupt request is from an external source via EXT INT or from the 3870's internal timer. Events are labeled with the letters A through G and are described below.

## Event A

An interrupt request must satisfy a hold time requirement as specified in the AC Characteristics in order to guarantee that it is valid on the rising edge of the WRITE clock.

# Event B

Event B represents the instruction being executed when the interrupt occurs. The last cycle of B is normally the instruction fetch for the next cycle. However, if B is not a privileged instruction and the CPU's Interrupt Control Bit is set, then the last cycle becomes a "freeze" cycle rather than a fetch. At the end of the freeze cycle the interrupt request latches are inhibited from altering the interrupt daisy-chain so that sufficient time will be allowed for the daisychain to settle. (If B is a privileged instruciton, the instruction fetch is not replaced by a freeze cycle; instead, the fetch is performed and the next instruction is executed. Although unlikely to be encountered, a series of privileged instructions will be sequentially executed without interrupt. One more instruction, called a 'protected' instruction, will always be executed after the last privileged instruction. The last cycle of the protected instruction then performs the freeze.)

I ne dashed lines on EXT INT illustrate the last opportunity for EXT INT to cause the last cycle of a non-protected instruction to become a freeze cycle.

The freeze cycle is a short cycle (4  $\Phi$  clock periods) in all cases except where B is the Decrement Scratchpad instruction, in which case the freeze cycle is a long cycle (6  $\Phi$  clock periods).

INT REQ goes low on the next negative edge of WRITE if both PRI IN is low and the appropriate interrupt enable bit of the Interrupt Control Part is set. Both INT REQ and WRITE are internal signals.

### Event C

A NO-OP long cycle to allow time for the internal priority chain to settle.

#### Event D

The program counter (P0) is pushed to the stack register (P) in order to save the return address. The interrupt circuitry places the lower 8 bits of the interrupt vector address onto the data bus. This is always a long cycle.

# Event E

A long cycle in which the interrupt circuitry places the upper 8 bits of the interrupt vector address onto the data bus.

# Event E

A long cycle in which the interrupt circuitry places the upper 8 bits of the interrupt vector address onto the data bus.

# Event F

A short cycle in which the interrupting interrupt request latch is cleared. Also, the CPU's Interrupt Control Bit is cleared, thus disabling interrupts until an EI instruction is performed. The fetch of the next instruction from the interrupt address.

# Event G

Begin execution of the first instruction of the interrupt service routine.

## Summary Of Interrupt Sequence

For the MK3870 the interrupt response time is defined as the time elapsed between the occurence of EXT INT going active (or the Timer transitioning to H'N') and the beginning of execution of the first instruction of the interrupt service routine. The interrupt response time is a variable depedent upon what the microprocessor is doing when the interrupt request occurs. As shown in Figure 5, the minimum interrupt response time is 3 long cycles plus 2 short cycles plus one WRITE clock pulse width plus a setup time of EXT INT prior to the leading edge of the WRITE pulse – a total of 27  $\Phi$  clock periods plus the setup time. At a 2 MHz  $\Phi$  this is 14.25  $\mu$ s. Although the maximum could theoretically be infinite, a practical maximum is 35  $\mu$ s (based on the interrupt request occurring near the beginning of a PI and LR K, P sequence).

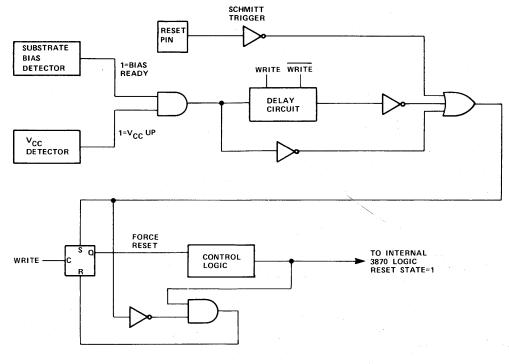

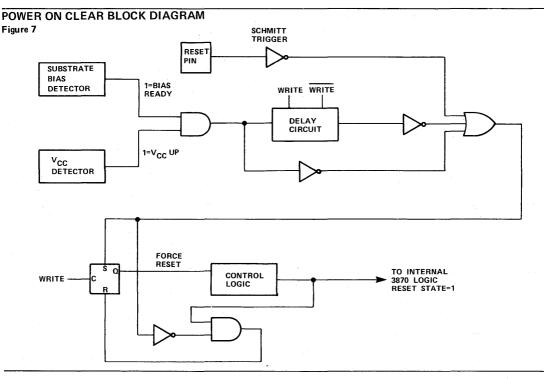

# **Power-On Clear**

The intent of the Power-On-Reset circuitry on the 3870 is to automatically reset the device following a typical power-up situation, thus saving external reset circuitry in many applications. This circuitry is not guaranteed to sense a "Brown Out" (low voltage) condition nor is it guaranteed to operate under all possible power-on situations.

Three conditions are required before the 3870 will leave the reset state and begin operation. Refer to Figure 7 as an aid to the following descriptions. The On-Chip Vcc detector senses a minimum value of Vcc before it will allow the 3870 to operate. The threshold of this detector is set by analog circuitry because a stable voltage reference is not available with n-channel MOS processing. Processing variations will cause this threshold to vary from a low of 3.0 volts to a high of 4.3 volts with 3.5 volts being typical. The 3870 uses a substrate bias as a technique to provide improved performance verses power consumption relative to conventional grounded substrate approaches. This bias generator may start operating as low as Vcc = 3 volts on some devices while others may require Vcc = 4 volts in order to get adequate substrate bias. Until the substrate reaches the proper bias, the 3870 will not be released from the reset state. The final condition required is that the clocks of the 3870 must be functioning. Typically the clocks will start to function at Vcc equal to 3 to 3.5 volts but since the part is tested at 4.5 volts MOSTEK cannot guarantee any operation below 4.5 volts. The output of the delay circuit in Figure 7 will stay low until the clocks start to function. If the input to the delay circuit is high, typically after 100 cycles of the WRITE clock (800 cycles of the external clock) the output of the delay circuit will go high allowing the 3870 to begin execution.

If Vcc falls to ground for at least a few hundred nanoseconds the output of the delay circuit will go low immediately and the 3870 will reset.

The internal logic may detect a valid Vcc, bias and clocks at Vcc = 3.5 volts and allow the 3870 to start executing after the time delay. With a slowly rising power supply the part may start running before Vcc is above 4.5 volts which is below the guaranteed voltage range. When power-on-clear is required with a slowly rising power supply, an external capacitor must be used on the RESET pin to hold it below 0.8 volts until Vcc is stable above 4.5 volts. (Note: The option to disconnect the internal pull-up resistor on RESET is available which allows the use of a larger external pull-up resistor and a small capacitor on RESET.)

In many applications, it is desirable if the unit does an automatic power-on-clear, but not mandatory. The unit will have a RESET push button and if the unit does not power-up correctly or malfuctions because of some disturbance on the Vcc line, the operator will simply press RESET and restore normal operation. It is for these applications that the internal power-onclear circuitry was designed.

In some applications it is required that the microcomputer continue to run properly without operator intervention after brown-outs, power line disturbances, electrical noise, computer malfunction due to a programming bug or any other disturbance except a catastrophic failure of some component.

Once concept used to keep computers running is that of the "WATCHDOG TIMER". The computer is programmed to periodically reset the watchdog timer during the normal execution of its program (this is easily done in the 3870 as its normal application is in some control function which is typically periodic). As long as the computer continues to execute its program the watchdog timer is continually reset and never times out. Should the computer stop executing its program for whatever reason, the watchdog timer will time out producing a RESET pulse to the CPU re-starting execution. This is a very positive way to assure that the computer is doing its job, i.e., executing the program. It is important that the software driving the watchdog timer test as many functional blocks (timer, ALU, scratchpad RAM, and Ports) of the 3870 as possible before reseting the watchdog timer. This is because operation of the 3870 with an out of spec power supply may allow some of the functions to operate correctly while other functions are not operable.

MOSTEK can guarantee correct operation of the 3870 only while the Vcc voltage remains within its specified limits. If proper operation of the 3870 must be guaranteed after a disturbance on the Vcc line, then an external circuit must be used to monitor the Vcc line and produce a RESET to the 3870 whenever Vcc is out of the specified limits.

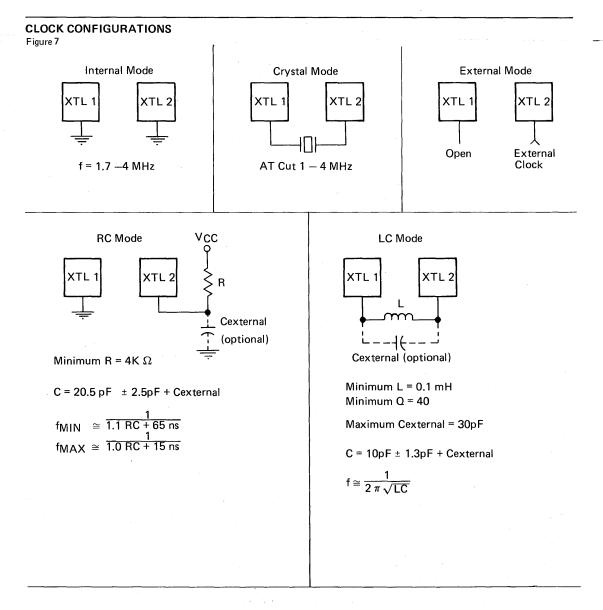

A related characteristic to power-on-clear is the Startup time of the basic timing element. The LC, and RC, oscillators begin to function almost immediately once Vcc is high enough to allow the onboard oscillator to operate (Vcc = 3.5). Operation with a crystal is partly mechanical and some start time is required to get the mass of the crystal into vibrational motion. This time is basically dependent on the frequency (mass) of the crystal. 4 MHz crystals typically require about 2-3 mSec to start while 1 MHz crystals require 60-70 mSec to start oscillating. Of course, this time may vary greatly from crystal to crystal and is also a function of the power supply rise time characteristic, however, the high frequency crystals start faster and are definately recommended (i.e., 3-4 MHz).

The condition of the port pins during the power-onclear sequence is often asked. The port pins or the STROBE line cannot be specified until Vcc reaches 4.5V and the 3870 enters the RESET state. Before this, the port pins may stay at Vss, may track Vcc as it rises, or they may track Vcc part way up then return to Vss (Ports 4 & 5 will go to Vcc once the clocks are running and the 3870 has sufficient Vcc to properly operate the internal control logic and I/O ports).

### **External Reset**

When RESET is taken low the content of the Program Counter is pushed to the Stack Register and then the Program Counter and the ICB bit of the W Status Register are cleared. The original Stack Register content is lost. Ports 4, 5, 6 and 7 are loaded

# INTERRUPT SEQUENCE Figure 6

# POWER ON CLEAR BLOCK DIAGRAM

Figure 7

SINGLE CHIP <sub>M</sub>C-2K ROM MX3870(P/N) with H '00'. The contents of all other registers and ports are unchanged or undefined. When RESET is taken high the first program instruction is fetched from ROM location H'000'. When an external reset of the 3870 occurs, PO is pushed into P and the old contents of P are lost. It must be noted that an external reset is recognized at the start of a machine cycle and not necessarily at the end of an instruction. Thus if the 3870 is executing a multicycle instruction, that instruction is not completed and the contents of P upon reset may not necessarily be the address of the instruction that would have been executed next. It may, for example, point to an immediate operand if the reset occurred during the second cycle of a LI or CI instruction. Additionally, several instructions (JMP, PI, PK, LR PO, Q) as well as the interrupt acknowledge sequence modify PO in parts. That is, they alter PO by first loading one part then the other and the entire operation takes more than one cycle. Should reset occur during this modification process the value pushed into P will be part of the old PO (the as yet unmodified part) and part of the new PO (already modified part). Thus care should be taken (perhaps by external gating) to insure that reset does not occur at an undesirable time if any significance is to be given to the contents of P after a reset occurs.

# Vcc Decoupling

The 3870 family devices have dynamic circuitry internally which requires a good high frequency decoupling capacitor to surpress noise on the Vcc line. A .01  $\mu$ F or .1  $\mu$ F ceramic capacitor should be placed between Vcc and ground, located physically close to the 3870 device. This will reduce noise generated by the 3870 to about 70-100mVolts on the Vcc line.

### **Test Logic**

Special test logic is implemented to allow access to the internal main data bus for test purposes.

In normal operation the TEST pin is unconnected or is connected to GND. When TEST is placed at a TTL level (2.0V to 2.6V) port 4 becomes an output of the internal data bus and port 5 becomes a wired-OR input to the internal data bus. The data appearing on the port 4 pins is logically true whereas input data forced on port 5 must be logically false. When TEST is placed at a high level (6.0V to 7.0V), the ports act as above and additionally the 2K x 8 program ROM is prevented from driving the data bus. In this mode operands and instructions may be forced externally through port 5 instead of being accessed from the program ROM. When <u>TEST</u> is in either the TTL state or the high state, <u>STROBE</u> ceases its normal function and becomes a machine cycle clock (identical to the F8 multi-chip system WRITE clock except inverted).

Timing complexities render the capabilities associated with the TEST pin impractical for use in a user's application, but these capabilities are thoroughly sufficient to provide a rapid method for thoroughly testing the 3870.

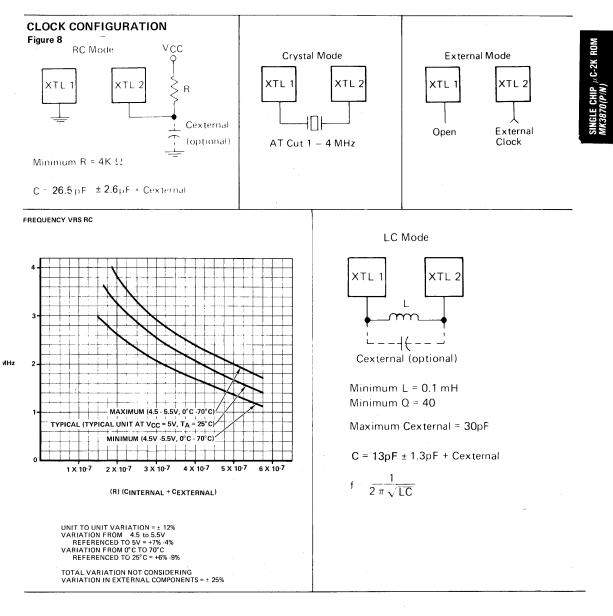

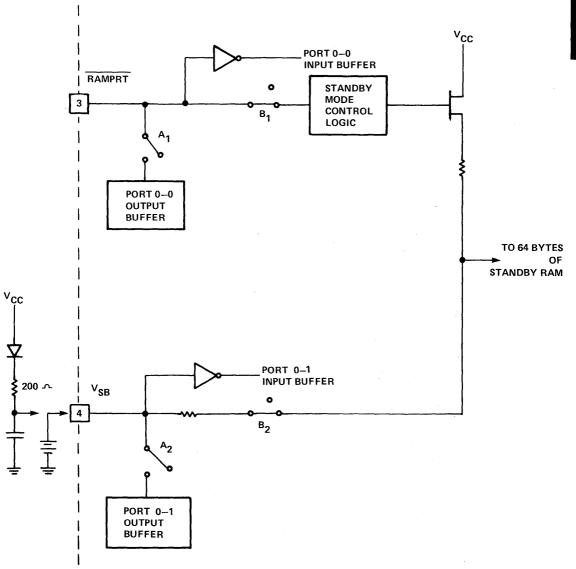

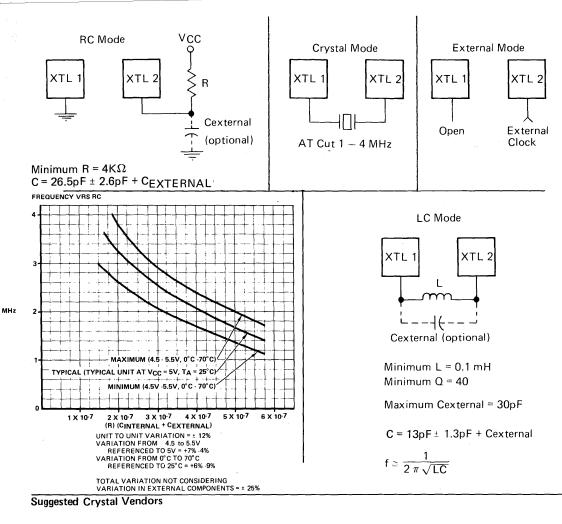

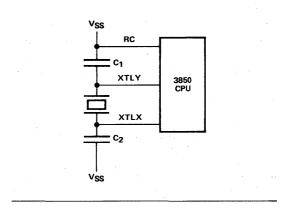

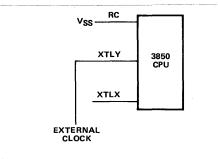

### 3870 Clocks

The time base for the 3870 may originate from one of four sources.

The four configurations are shown in Figure 8. There is an internal 26pF capacitor between XTL 1 and GND and an internal 26pF capacitor between XTL 2 and GND. Thus external capacitors are not neccesarily required. In all external clock modes the external time base frequently is divided by two to form the internal  $\Phi$  clock.

#### **Crystal Selection**

The use of a crystal as the time base is highly recommended as the frequency stability and reproducability from system to system is unsurpassed. The 3870 has an internal divide by two to allow the user of inexpensive and widely available TV Color Burst Crystals (3.58MHz). The following crystal parameters and vendors are suggested for 3870 applications:

#### Parameters

- a) Parallel Resonance, Fundamental Mode AT-Cut, HC-33/ $\mu$  holder

- b) Frequency Tolerance measured with 18pF load (0.1% accuracy). Drive level 10mW.

- c) Shunt Capacitance (Co) = 7pF max.

- d) Series Resistance (Rs)

| f = 1MHz    | Rs = 550 ohms max. |

|-------------|--------------------|

| f = 2MHz    | Rs = 300 ohms max. |

| f = 3MHz    | Rs = 100 ohms max. |

| f = 3.58MHz | Rs = 100 ohms max. |

| f = 4MHz    | Rs = 100 ohms max. |

### Suggested Crystal Vendors

- a) Electro-Dynamics 5625 Foxridge Drive Mission, Kansas 66201 913-262-2500

- b) CRYSTEK 1000 Crystal Drive Ft. Myers, Florida 33901 813-936-2109

- c) W.T. Liggett Corp. 1500 Worcester Rd. Section 30 Framingham, MA 01701 617-620-1150

- d) Erie Frequency Control 453 Lincoln Street Carlisle, Penn 17013 717-249-2232

- e) Electronic Crystals Corp. 1153 Southwest Blvd. Kansas City, Kansas 66103 913-262-1274

- f) M-TRON Industries P.O. Box 630 100 Douglas Avenue Yankton, South Dakota 605-665-9321

MK3870 PROGRAMMING MODEL

18

# SINGLE CHIP $\mu$ C-2K ROM mK3870(P/N)

# INSTRUCTION EXECUTION

This section details the timing and execution of the 3870 instruction set. The 3870 executes the entire F8 instruction set with exact F8 timing. Refer to Figure 11 for a 3870 Programming Model.

# **F8 INSTRUCTION SET**

# ACCUMULATOR GROUP INSTRUCTIONS

| DPERATION              | MNEMONIC<br>OP CODE | OPERAND | FUNCTION       | MACHINE<br>CODE | BYTES | CYC<br>SHORT | LES<br>LONG | ルS<br>(2MHz中) | OVR | STATU<br>ZERO | S BITS<br>CRY | SIGN |

|------------------------|---------------------|---------|----------------|-----------------|-------|--------------|-------------|---------------|-----|---------------|---------------|------|

|                        |                     |         |                |                 |       |              |             | -             |     |               |               |      |

| Add Carry              | LNK                 |         | A+(A) + CRY    | 19              | 1     | 1            |             | 2             | 1/0 | 1/0           | 1/0           | 1/0  |

| Add Immediate          | AI                  | н       | A+(A) + H ′u′  | 24              | 2     | 1            | 1           | 5             | 1/0 | 1/0           | 1/0           | 1/0  |

| And Immediate          | NI                  | н       | A≁(A)VH.,⊓,    | 210             | 2     | 1            | 1           | 5             | 0   | 1/0           | 0             | 1/0  |

| Slear                  | CLR                 |         | A⇒H'00'        | 70              | 1     | 1            |             | 2             | -   | _             | -             | -    |

| Compare Immediate      | CI                  | 0       | H'u'+ (A) + 1  | 25              | 2     | 1            | 1           | 5             | 1/0 | 1/0           | 1/0           | 1/0  |

| Complement             | COM                 |         | A⇒(A) + H'FF'  | 18              | 1     | 1            |             | 2             | 0   | 1/0           | 0             | 1/0  |

| Exclusive or Immediate | XI                  | ú       | A⇒(A) · H'a'   | 230             | 2     | 1            | T           | 5             | 0   | 1/0           | 0             | 1/0  |

| ncrement               | INC                 |         | A →(A) + 1     | 1 <i>F</i>      | 1     | 1            |             | 2             | 1/0 | 1/0           | 1/0           | 1/0  |

| Load Immediate         | LI                  | 0       | A <b></b> H'u' | 20              | 2     | 1            | 1           | 5             | -   | -             | -             |      |

| Load Immediate Short   | LIS                 | 1       | A+H' 0i'       | 71              | 1     | 1            |             | 2             |     |               |               |      |

| OR Immediate           | 01                  | п       | A≁(A) V H 'u'  | 220             | 2     | 1            | 1           | 5             | 0   | 1/0           | 0             | 1/0  |

| Shift Left One         | SL                  | 1       | Shift Left 1   | 13              | 1     | 1            |             | 2             | 0   | 1/0           | 0             | 1/0  |

| Shift Left Four        | SL                  | 4       | Shift Left 4   | 15              | 1     | 1            |             | 2             | 0   | 1/0           | 0             | 1/0  |

| Shift Right One        | SR                  | 1       | Shift Right 1  | 12              | 1     | 1            |             | 2             | 0   | 1/0           | 0             | 1 .  |

| Shift Right Four       | SR                  | 4       | Shift Right 4  | 14              | 1     | 1            |             | 2             | 0   | 1/0           | 0             | 1    |

# **BRANCH INSTRUCTIONS** In all conditional branches $P0 \leftarrow (P0) + 2$ if the test condition is not met. Execution is complete in 3 short cycles.

|                           | MNEMONIC          |                               |                                    | MACHINE       |       | CYCLES |      | μS      |     | STATUS BITS |                |      |

|---------------------------|-------------------|-------------------------------|------------------------------------|---------------|-------|--------|------|---------|-----|-------------|----------------|------|

| OPERATION                 | OP CODE           | OPERAND                       | FUNCTION                           | CODE          | BYTES | SHORT  | LONG | (2MHz中) | OVR | ZERO        | CRY            | SIGN |

|                           |                   |                               |                                    |               |       |        |      |         |     |             |                |      |

| Branch on Carry           | вс                | aa                            | P0→(P0)+1+ H'aa' if CRY            | 82aa          | 2     | 2      | 1    | 7       | _   |             | → <sup>`</sup> | -    |

| Branch on Positive        | BP                | aa                            | P0 ♣ (P0) + 1 + H'aa ' if          | 81aa          | 2     | 2      | 1    | 7       | _   | —           |                |      |

|                           |                   |                               | SIGN 1                             |               |       |        |      |         |     |             |                |      |

| Branch on Zero            | вZ                | aa                            | P0 → (P0) + 1 + H'aa' if<br>Zero 1 | 8 <b>4</b> aa | 2     | 2      | 1    | 7       | -   | -           | -              | _    |

| Branch on True            | вт                | taa                           | P0++(P0) + 1 + H'aa '              | 8taa          | 2     | 2      | 1    | 7       | _   | -           | _              | _    |

|                           | 22                | CONDITION<br>2 20<br>CRY SIGN | if any test is true                |               |       |        |      |         |     |             |                |      |

| Branch If Negative        | 8M                | за                            | P0++(P0)+1+H'aa'                   | 91aa          | 2     | 2      | 1    | 7       | _   | -           |                | _    |

| L                         |                   |                               | IFSIGN 0                           |               |       |        |      |         |     |             |                |      |

| Branch of No Carry        | BNC               | aa                            | P0→ (P0) +1+ H'aa '                | 92aa          | 2     | 2      | 1    | 7       |     | -           |                | -    |

|                           |                   |                               | ICARRY 0                           |               |       |        |      |         |     |             |                |      |

| Branch if No Overflow     | BNO               | aa                            | P0 + (P0) + 1 + H'aa               | 98aa          | 2     | 2      | 1    | 7       |     | _           | -              | _    |

|                           |                   |                               | IFOVR 0                            |               |       |        |      |         |     |             |                |      |

| Branch if Not Zero        | BNZ               | aa                            | P0 ← (P0) + 1 + H'aa '             | <b>94</b> aa  | 2     | 2      | 1    | 7       | -   | -           |                |      |

|                           |                   |                               | I ZERO O                           |               |       |        |      |         |     |             |                |      |

| Branch if False Test      | BF                | taa                           | P0 🗢 (P0) +1+ H'aa '               | 9taa          | 2     | 2      | 1    | 7       |     | _           |                | _    |

|                           |                   | 2' Z'                         | if all false test bits             |               |       |        |      |         |     |             |                |      |

| Branch if ISAR (Lower) /7 | OVF ZERO C<br>BR7 | aa                            | P0→ (P0)+1+ H'aa ' if              | 8Faa          | 2     | 2      | 1    | 5       | _   | ,           |                |      |

|                           |                   |                               | ISARL /7                           |               |       |        |      |         |     |             |                |      |

|                           |                   |                               | P0 + (P0) +2 / ISARL =             | `             | 2     | 2      |      | 4       | -   | _           | _              | -    |

| Branch Relative           | BR                | aa                            | P0 - (P0)+1+ H'aa '                | 90aa          | 2     | 2      | 1    | 7       | -   | _           | _              | _    |

| Jump*                     | JMP               | aaaa                          | P0 ←H'aaaa'                        | 29aaaa        | 3     | 1      | 3    | 11      |     |             |                |      |

# MEMORY REFERENCE INSTRUCTIONS In all Memory Reference Instructions, the Data Counter is incremented DC -(DC)+1

| OPERATION   | MNEMONIC     |                           | MACHINE |       | CYC   | LES  | μS       | STATUS BITS |      |     |      |

|-------------|--------------|---------------------------|---------|-------|-------|------|----------|-------------|------|-----|------|

|             | OP CODE OPER | AND FUNCTION              | CODE    | BYTES | SHORT | LONG | (2MHz(P) | OVR         | ZERO | CRY | SIGN |

| ·····       |              |                           |         |       |       |      |          |             |      |     |      |

| Add Binary  | AM           | A+(A) + [(DC)]            | 88      | 1     | 1     | 1    | 5        | 1/0         | 1/0  | 1/0 | 1/0  |

| Add Decimal | AMD          | A <b>→</b> (A) + [(DC)] • | 89      | 1     | 1     | 1    | 5        | 1/0         | 1/0  | 1/0 | 1/0  |

|             |              | BCD Adjust                |         |       |       |      |          |             |      |     |      |

| AND         | NM           | A-(A) ∧ [(DC)]            | 8A      | 1.1   | 1     | 1    | 5        | 0           | 1/0  | 0   | 1/0  |

| Compare     | CM           | [(DC)] + (A) + 1          | 8D      | 1     | 1     | 1    | 5        | 1/0         | 1/0  | 1/0 | 1/0  |

| xclusive OR | ×M           | A <b>⊲</b> (A)() (DC)]    | 8C      | 1     | 1     | 1    | 5        | 0           | 1/0  | 0   | 1/0  |

| _oad        | LM           | A-((DC))                  | 16      | 1     | ۱     | 1    | 5        | -           | -    | -   | -    |

| Logical OR  | OM           | A≪ (A) V ((DC)]           | 88      | 1     | 1     | 1    | 5        | 0           | 1/0  | 0   | 1/0  |

| Store       | ST           | A -= [(DC)]               | 17      | 1     | 1     | 1    | 5        |             | _    | _   | _    |

# ADDRESS REGISTER GROUP INSTRUCTIONS

|                               | MNEMONIC |         |                                     | MACHINE |       | CYC   | LES  | μS      |     | STATUS BITS |     |      |  |

|-------------------------------|----------|---------|-------------------------------------|---------|-------|-------|------|---------|-----|-------------|-----|------|--|

| OPERATION                     | OP CODE  | OPERAND | FUNCTION                            | CODE    | BYTES | SHORT | LONG | (2MHz中) | OVR | ZERO        | CRY | SIGN |  |

| Addi to Data Counter          | ADC      |         | DC+(DC) + (A)                       | 8E      | 1     | 1     | 1    | 5       | -   | -           | -   | -    |  |

| Call to Subroutine*           | РК       |         | POU+(12); POL+(13), P+(P0)          | oc      | 1     | 1     | 2    | 8       | -   | -           | -   | -    |  |

| Call to Subroutine Immediate* | P1       | aaaa    | P <b>→</b> (PO), PO <b>→</b> H'aaaa | 28aaaa  | 3     | 2     | 3    | 13      | -   |             | -   | -    |  |

| Exchange DC                   | XDC      |         | (DC) (DC1)                          | 2C      | 1     | 2     |      | 4       | -   | ~           | -   | ·    |  |

| Load Data Counter             | LR .     | DC,O    | DCU≪(14), DCL€((15)                 | OF      | 1     | 1     | 2    | 8       | _   | -           | -   | -    |  |

| Load Data Counter             | LR       | DC.H    | DCU=(10), DCL=((11)                 | 10      | 1     | 1     | 2    | 8       | -   | _           | -   | -    |  |

| Load DC Immediate             | DCI      | deda    | DC H'aaaa'                          | 2Aaaaa  | 3     | 3     | 2    | 12      | -   | _           | -   | _    |  |

| Load Program Counter          | LR       | P0.0    | P0U≠(14), P0L≠(+15)                 | 00      | 1     | 1     | 2    | 8       | _   | _           | -   | _    |  |

| Load Stack Register           | LR       | P,K     | PU=(r12), PL=(r13)                  | 09      | 1     | 1     | 2    | 8       | _   |             | -   | -    |  |

| Return from Subroutine*       | POP      |         | PO (P)                              | 1C      | 1 1   | 2     |      | 4       | _   | _           | -   | _    |  |

| Store Data Counter            | LR       | 0.DC    | (14+(9CU). (15+(DCL)                | OE      | 1     | 1     | 2    | 8       |     | -           | _   | _    |  |

| Store Data Counter            | LR       | H,DC    | r10+DCU), r11+(DCL)                 | 11      | 1     | 1.    | 2    | 8       |     | -           | ~   |      |  |

| Store Stack Register          | LR       | K,P     | 12+(PU); 13+(PL)                    | 08      | 1     | 1     | 2    | 8       | -   |             | _   | -    |  |

## SCRATCHPAD REGISTER INSTRUCTIONS (Refer to Scratchpad Addressing Modes)

| OPERATION    | MNEMONIC<br>OP CODE | OPERAND     | FUNCTION                 | MACHINE<br>CODE | BYTES | CYC<br>SHORT | LES | μS<br>(2MHzΦ) | OVR | STATU<br>ZERO | S BITS<br>CRY | SIGN |

|--------------|---------------------|-------------|--------------------------|-----------------|-------|--------------|-----|---------------|-----|---------------|---------------|------|

| Add Binary   | AS                  | ,           | A+(A)+ (r)               | Ci              | 1     | 1            |     | 2             | 1/0 | 1/0           | 1/0           | 1/0  |

| Add Decimal  | ASD                 | ı.          | A+(A) + (r)              | Dr              | 1     | 2            |     | 4             | 1/0 | 1/0           | 1/0           | 1/0  |

| Decrement    | DS                  | 1           | (+(r) (H'FF'             | 31              | 1     |              | 1   | 3             | 1/0 | 1/0           | 1/0           | 1/0  |

| Load         | LR                  | A,1         | A <b>→</b> (1)           | 41              | 1     | 1            |     | 2             | -   | -             |               | -    |

| Load         | LR                  | A, KU       | A= (112)                 | 00              | 1     | 1            |     | 2             | -   | ~             |               |      |

| Load         | LR                  | A, KL       | A+((13)                  | 01              | 1     | 1            |     | 2             | -   | -             | -             |      |

| Load         | LR                  | A, OU       | A ⇒(i 14)                | 02              | 1     | 1            |     | 2             | _   | -             | _             |      |

| Load         | LR                  | A, QL       | A                        | 03              | 1     | 1            |     | 2             | _   | -             |               |      |

| Load         | LR                  | т, <b>А</b> | ( 🖬 ( A )                | 51              | 1     | 1            |     | 2             | -   | -             | _             | _    |

| Load         | LR                  | KU, A       | 12 <del>4</del> (A)      | 04              | 1     | 1            |     | 2             | -   | -             | _             | _    |

| Load         | LR                  | KL, A       | (13 <b>→</b> (A)         | 05              | -1    | 1            |     | 2             | -   | -             | _             |      |

| Load         | LR                  | QU, A       | 14 <b>→</b> (A)          | 06              | 1     | 1            |     | 2             |     | _             | -             | _    |

| Load         | LR                  | OL,A        | r15⊶(A)                  | 07              | 1     | 1            |     | 2             | -   | -             | -             |      |

| And          | NS                  | 1           | A - (A) ∧ (r)            | Fr              | 1.    | 1            |     | 2             | 0   | 1/0           | 0             | 1/0  |

| Exclusive Or | xs                  |             | $A \leftarrow (A) + (r)$ | Er              | - 1   | 1            |     | 2             | 0   | 1/0           | 0             | 1/0  |

\*Privileged instruction, Accumulator contents altered during execution of PI instruction.

# MISCELLANEOUS INSTRUCTIONS

|                        | MNEMONIC |             |                       | MACHINE   |       | CYC   | LES  | μS      |               | STATUS | SBITS |          |

|------------------------|----------|-------------|-----------------------|-----------|-------|-------|------|---------|---------------|--------|-------|----------|

| OPERATION              | OP CODE  | OPERAND     | FUNCTION              | CODE      | BYTES | SHORT | LONG | (2MHz中) | OVR           | ZERO   | CRY   | SIGN     |

| Disable Interrupt      | DI       |             | RESET ICB             | 1A        | 1     | 1     |      | 2       | -             |        | _     | -        |

| Enable Interrupt *     | EI       |             | SET ICB               | 1B        | 1     | 1     |      | 2       | -             | -      | -     | -        |

| Input                  | IN       | 04,05,06,07 | A⊶(Input Port aa)     | 26aa      | 2     | 1     | 2    | 8       | 0             | 1/0    | 0     | 1/0      |

| Input Short            | INS      | 0, 1        | A.←(Input Port 0 or   | 1) A0,A1  | 1     | 2     |      | 4       | 0             | 1/0    | 0     | 1/0      |

| Input Short            | INS      | 4,5,6,7     | A ←(Input Port a)     | Aa        | 1     | 1     | 2    | 8       | 0             | 1/0    | 0     | 1/0      |

| Load ISAR              | LR       | IS,A        | IS <del>∡</del> (A)   | 0B        | 1     | 1     |      | 2       | <u> </u>      |        | -     | -        |

| Load ISAR Lower        | LISL     | bbb         | ISL <del>≪</del> -bbb | 6(0bbb)** | 1     | 1     |      | 2       |               | -      | -     | _        |

| Load ISAR Upper        | LISU     | bbb         | ISU <del>≺</del> bbb  | 6(1bbb)** | 1     | 1     |      | 2       | -             | _      | _     | _        |

| Load Status Register * | LR       | W,J         | W <del>∢</del> (r9)   | 1D        | 1     | 2     |      | 4       | 1/0           | 1/0    | 1/0   | 1/0      |

| No Operation           | NOP      |             | P0 <b>←</b> (P0) + 1  | 2B        | 1     | 1     |      | 2       | -             | _      |       | -        |

| Output *               | OUT      | 04,05,06,07 | Output Port aa-(A)    | 27aa      | 2     | 1     | 2    | 8       | -             | _ `    |       | · —      |

| Output Short           | OUTS     | 0, 1        | Output Port           | BO, B1    | t     | 2     |      | 4       | -             | _      | _     | -        |

|                        |          |             | 0 or 1 <b>→</b> (A)   |           |       |       |      |         |               |        |       |          |

| Output Short           | OUTS     | 4,5,6,7     | Output Port a⊶(A)     | Ba        | 1 、   | 1     | 2    | 8       | -             | -      |       | <u> </u> |

| Store ISAR             | LR       | A,IS        | A <b>⊸</b> (IS)       | 0A        | 1     | 1     |      | 2       | <del></del> . | -      | _     | -        |

| Store Status Reg       | LR       | J,W         | r9 <b>←</b> (W)       | 1E        | 1     | 1     |      | 2       |               | -      |       |          |

\*\*b = 1 bit immediate operand

#### NOTES.

| Lower ca        | se denotes variables specified by programmer       | KL           | Register 13                                            |

|-----------------|----------------------------------------------------|--------------|--------------------------------------------------------|

|                 |                                                    | ĸu           | Register 12                                            |

| Function        | Definitions                                        | РÛ           | Program Counter                                        |

|                 | •                                                  | POL          | Least Significant 8 bits of Program Counter            |

| <b>-</b>        | is replaced by                                     | POU          | Most Significant 8 bits of Program Counter             |

| ()              | the contents of                                    | Р            | Stack Register                                         |

| $\overline{()}$ | Binary "1's" complement of                         | PL           | Least Significant 8 bits of Program Counter            |

| +               | Arithmetic Add (Binary or Decimal)                 | PU           | Most Significant 8 bits of Active Stack Register       |

| Ð               | Logical "OR" exclusive                             | Q            | Registers 14 and 15                                    |

| Ň               | Logical "AND"                                      | QL           | Register 15                                            |

| Ŷ               | Logical "OR" inclusive                             | QU           | Register 14                                            |

| н' '            | Hexadecimal digit                                  | r            | Scratchpad Register (any address 0 thru B) (See Below) |

| [()]            | Contents of memory specified by ()                 | w            | Status Register                                        |

| а               | Address Variable (four bits)                       | Scratchpa    | d Addressing Modes Using IS. ( $r \neq 0$ thru B)      |

| А               | Accumulator                                        | • ·          | ······································                 |

| b               | One bit immediate operand                          | r=H'C'       | Register Addressed by IS is (Unmodified)               |

| DC              | Data Counter (Indirect Address Register)           | r=H'D'       | Register Addressed by IS is Incremented                |

| DC1             | Data Counter 1 (Auxiliary Data Counter)            | r≃H'E'       | Register Addressed by IS is Decremented                |

| DCL             | Least significant 8 bits of Data Counter Addressed | r=H'F'       | Illegal OP Code.                                       |

| DCU             | Most significant 8 bits of Data Counter Addressed  |              |                                                        |

| н               | Scratchpad Register 10 and 11                      | Status Reg   | lister                                                 |

| i               | Immediate operand (four bits)                      |              |                                                        |

| ICB             | Interrupt Control Bit                              | _            | No change in condition                                 |

| 1S              | Indirect Scratchpad Address Register               | 1/0          | is set to "1" or "0" depending on conditions           |

| ISL             | Least Significant 3 bits of ISAR                   | CRY          | Carry Flag                                             |

| ISU             | Most Significant 3 bits of ISAR                    | OVB          | Overflow Flag                                          |

| J               | Scratchpad Register 9                              |              |                                                        |

| к               | Registers 12 and 13                                |              | • •                                                    |

| -               |                                                    | SIGN<br>ZERO | Sign of Result Flag<br>Zero Flag                       |

# ELECTRICAL SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS\*

| Temperature Under Bias                                             | 0°C to 70°C      |

|--------------------------------------------------------------------|------------------|

| Storage Temperature                                                | .–65°C to +150°C |

| Voltage on Any Pin With Respect To Grouns (except open drain pins) |                  |

| Voltage On Open Drain Pins                                         |                  |

| Power Dissipation                                                  |                  |

| Power Dissipated by any one I/O pin <sup>4</sup>                   |                  |

| Power Dissipated by all I/O pins <sup>4</sup>                      |                  |

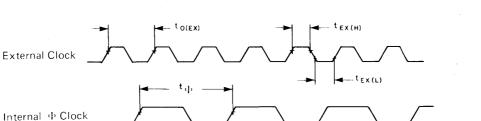

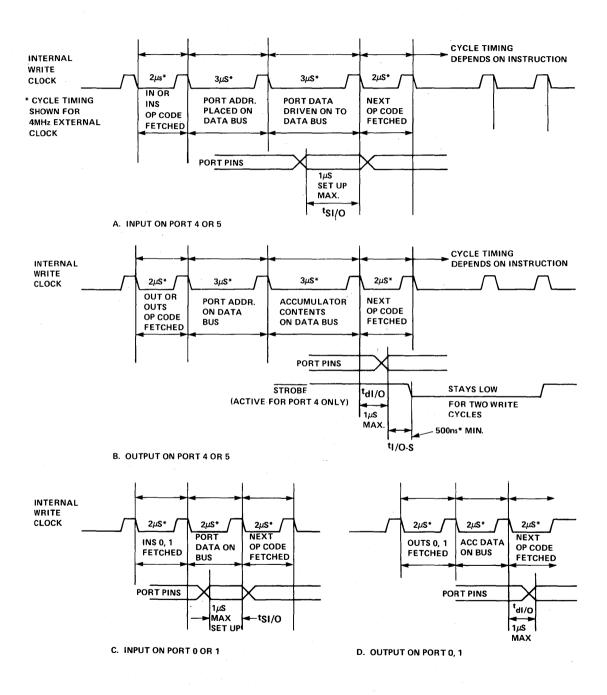

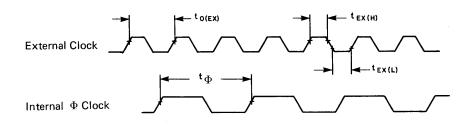

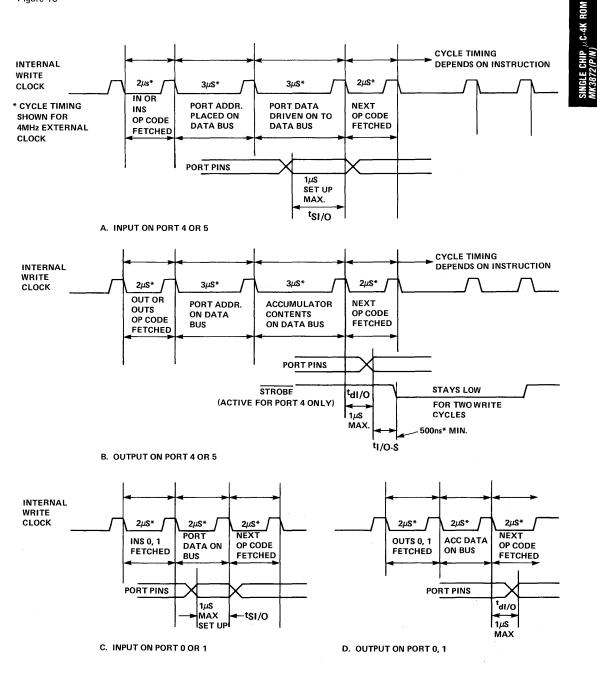

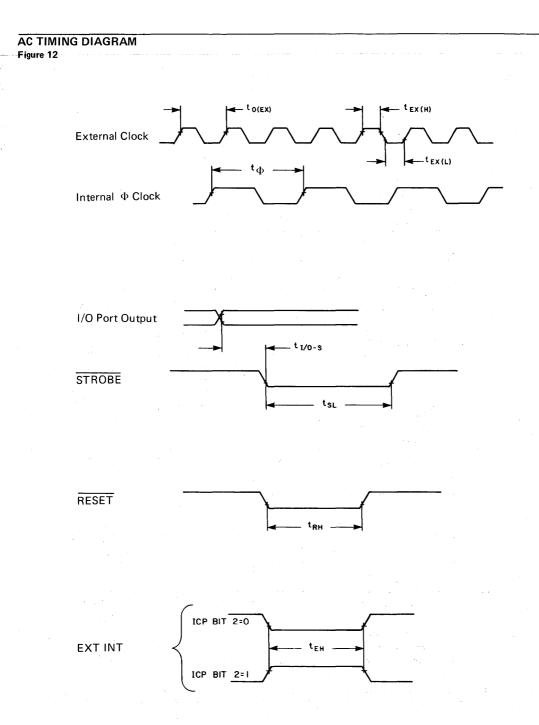

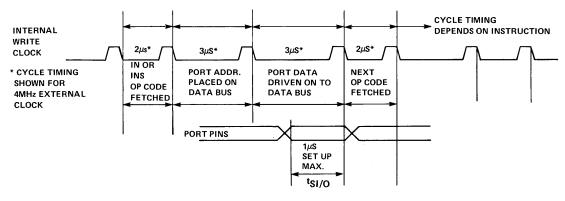

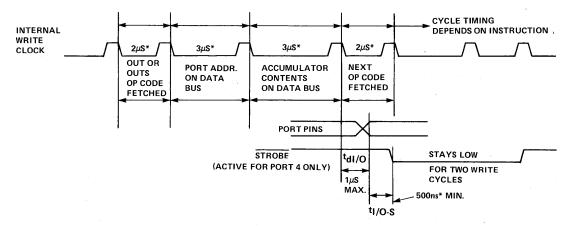

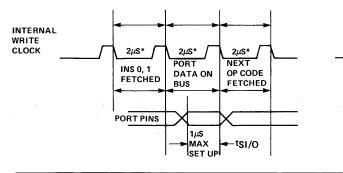

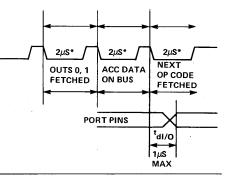

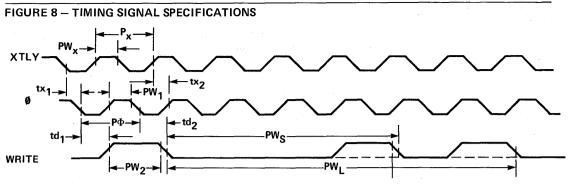

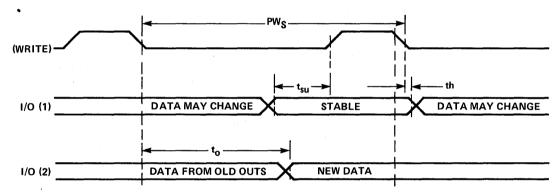

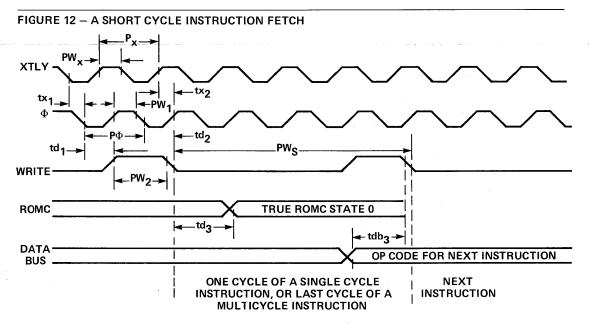

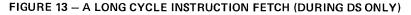

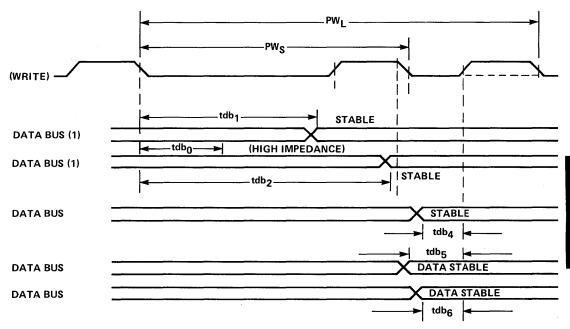

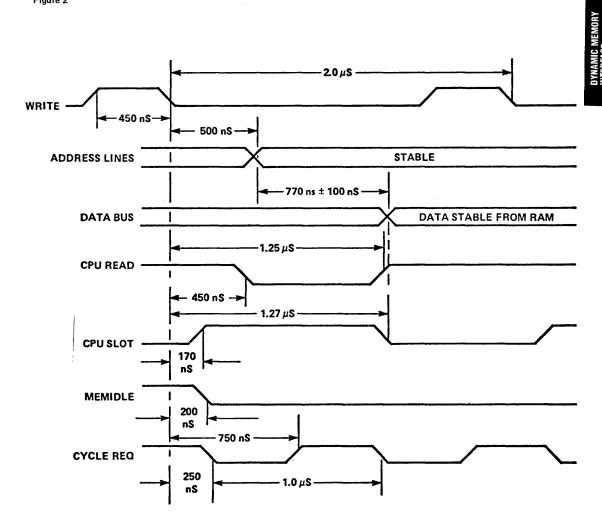

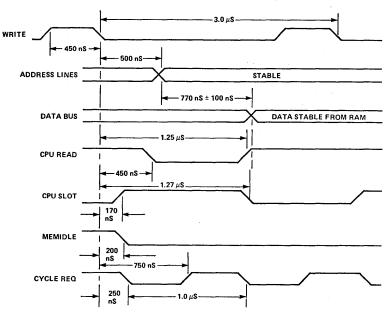

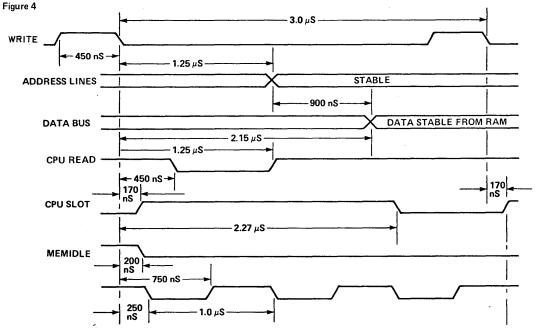

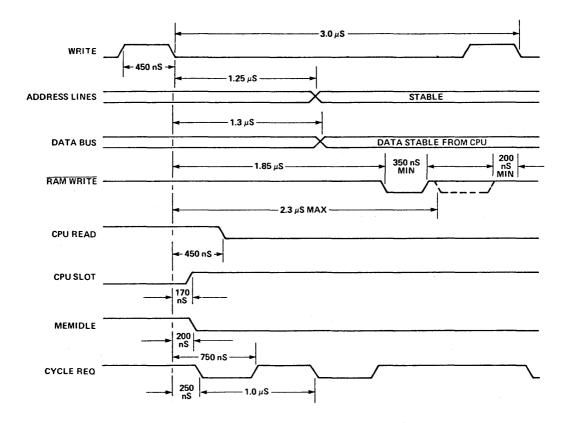

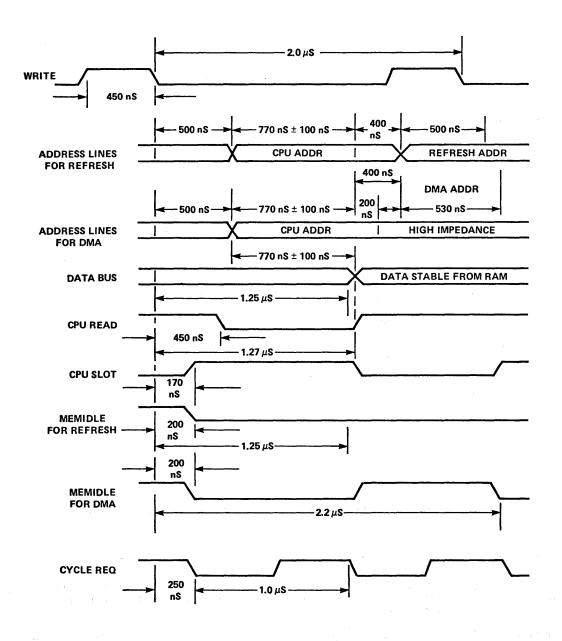

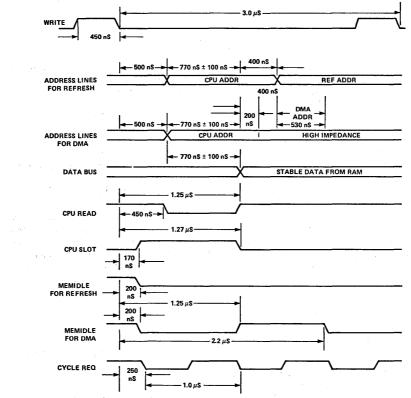

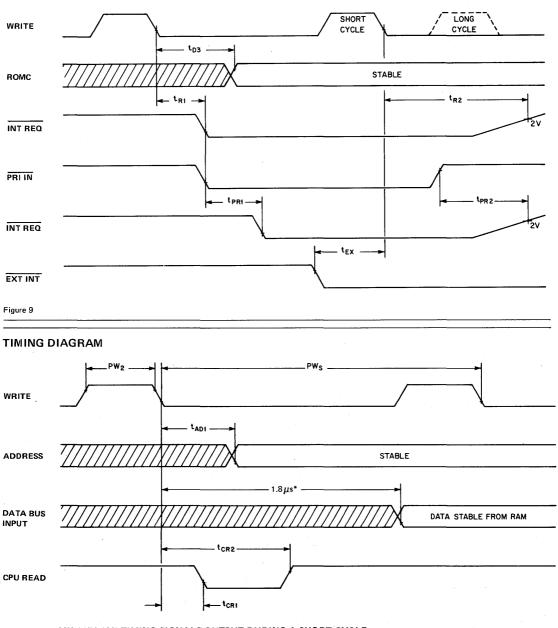

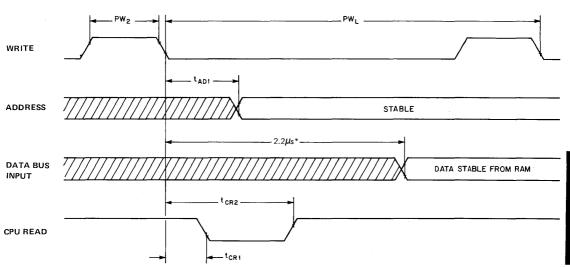

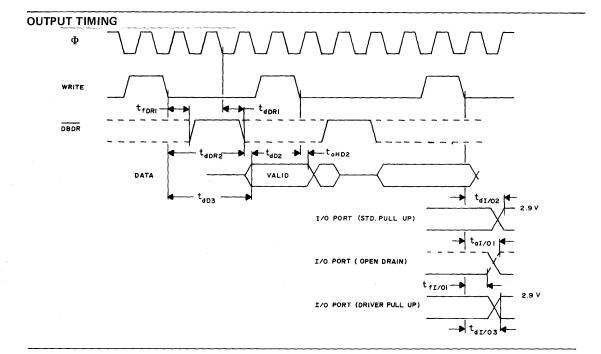

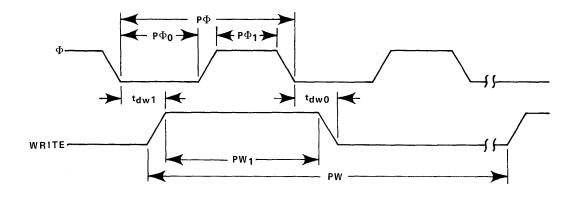

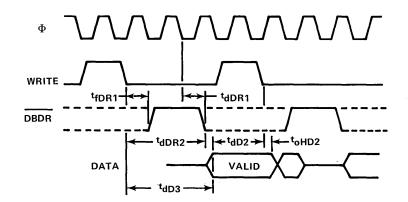

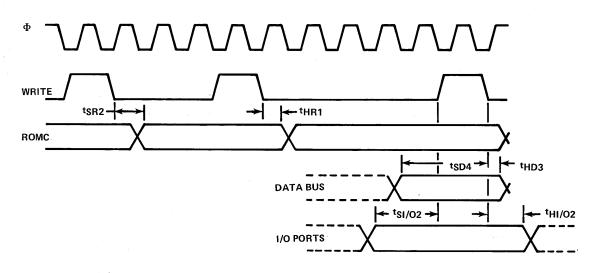

# A.C. CHARACTERISTICS - See Figure 12 and 13 for Timing Diagrams

| SIGNAL         | SYMBOL                                    | PARAMETER                                                             | MIN                    | МАХ              | UNIT     | NOTES                                                      |  |

|----------------|-------------------------------------------|-----------------------------------------------------------------------|------------------------|------------------|----------|------------------------------------------------------------|--|

|                | t <sub>O</sub> (INT)                      | Time Base Period,<br>internal oscillator                              | 250                    | 1000             | ns       | 4MHz - 1.0MHz                                              |  |

| XTL 1<br>XTL 2 | t <sub>O</sub> (EX)<br><sup>t</sup> EX(H) | Time base period, all<br>external modes<br>External Clock Pulse Width | 250                    | 1000             | ns       | 4MHz-1MHz                                                  |  |

|                | <sup>t</sup> EX(L)                        | High<br>External Clock Pulse Width Low                                | 90<br>100              | 700<br>700       | ns<br>ns |                                                            |  |

| ф              | t <sub></sub>                             | Internal $\Phi$ Clock Period                                          | 2                      | 2 <sup>t</sup> 0 |          | <u> </u>                                                   |  |

| WRITE          | tw                                        | Internal WRITE Clock Period                                           | 4t <sub>Փ</sub><br>6tφ |                  |          | Short Cycle<br>Long Cycle                                  |  |

| 1/0            | tdi/O                                     | Output delay from<br>internal WRITE Clock                             | 0                      | 1000             | ns       | 50pF plus<br>one TTL load                                  |  |

|                | t <sub>sl</sub> /O                        | Input Setup time<br>to WRITE Clock                                    | 1000                   |                  | ns       |                                                            |  |

|                | tI/O-s                                    | Output valid to STROBE<br>Delay                                       | 3t∳<br>-1000           | 3t∳<br>+250      |          | I/O load =<br>50pF + 1 TTL<br>STROBE Load=<br>50pF + 3 TTL |  |

| STROBE         | tsl                                       | STROBE Low Time                                                       | 8tΦ<br>-250            | 12tΦ<br>+250     | ns       |                                                            |  |

| RESET          | <sup>t</sup> RH                           | RESET Hold Time, Low                                                  | 6tΦ<br>+750            |                  | ns       |                                                            |  |

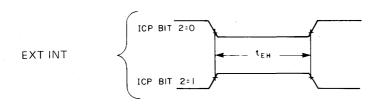

| EXT INT        | <sup>t</sup> EH                           | EXT INT Hold Time,                                                    | 6tΦ +<br>750           |                  | ns       | To trigger<br>interrupt                                    |  |

|                |                                           | Active and Inactive State                                             | 2tΦ                    |                  |          | To trigger<br>timer                                        |  |

# TA = 0°C to 70°C, VCC = 5V $\pm$ 10%, I/O POWER DISSIPATION $\leqslant$ 100mW

# CAPACITANCE

$T_A = 25^{\circ}C$ , f=2MHz

| SYMBOL           | PARAMETER                                                    | MIN  | MAX  | UNIT | NOTES              |

|------------------|--------------------------------------------------------------|------|------|------|--------------------|

| C <sub>IN</sub>  | Input Capacitance: I/O Ports, RESET,<br>EXTINT, RAMPRT, TEST |      | 7    | pF   | Unmeasured<br>Pins |

| C <sub>XTL</sub> | Input Capacitance: XTL1, XTL2                                | 20.5 | 32.5 | pF   | Grounded           |

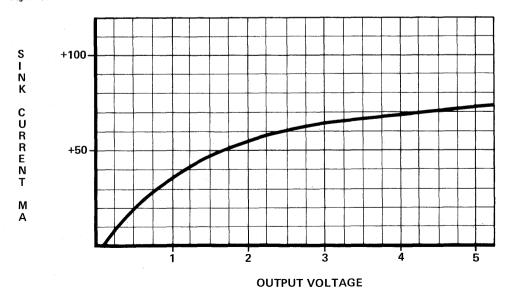

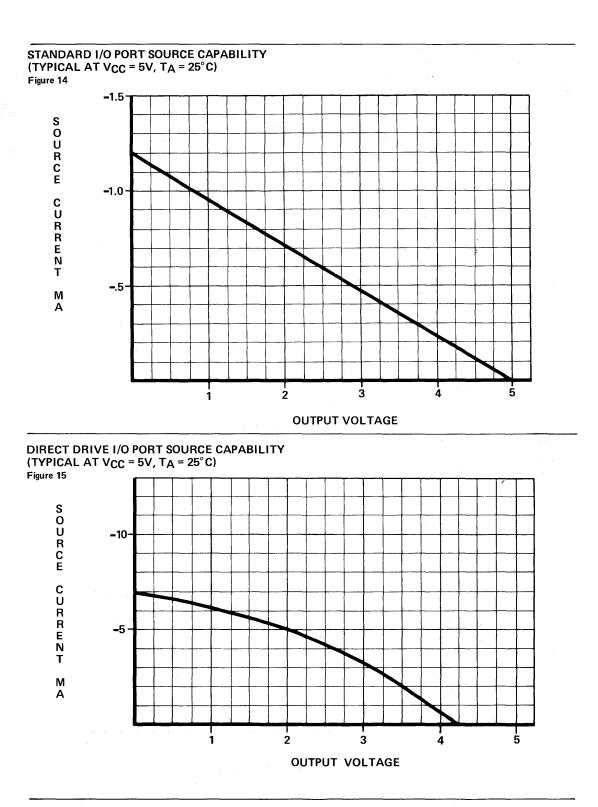

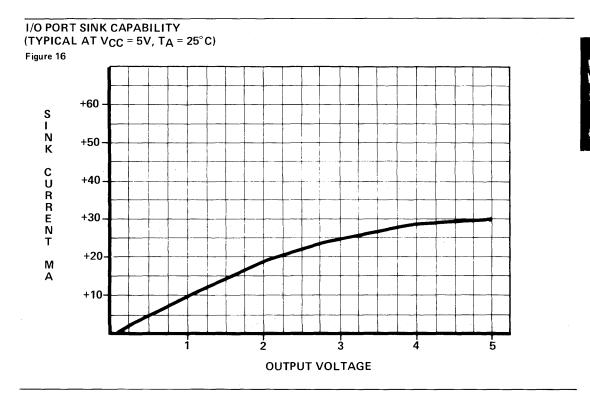

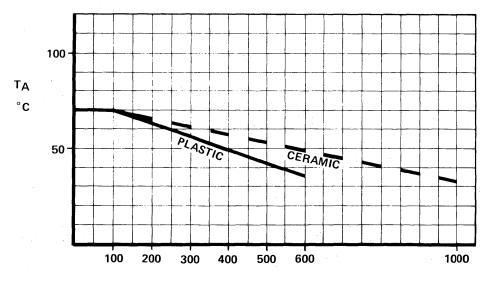

DC CHARACTERISTICS - See Figures 12-17 for typical curves.

# $T_{A}$ = 0° C to 70° C, V\_{CC} = +5V $\pm\,$ 10%, I/O POWER DISSIPATION $\leqslant$ 100mW

| SYMBOL           | PARAMETER                                                                                | MIN         | MAX       | UNIT     | TEST CONDITIONS                                 |

|------------------|------------------------------------------------------------------------------------------|-------------|-----------|----------|-------------------------------------------------|

| lcc              | Power Supply Current                                                                     |             | 85        | mA       | Outputs Open                                    |

| PD               | Power Dissipation                                                                        |             | 400       | mW       | Outputs Open                                    |

| VIHEX            | External Clock<br>Input High Level                                                       | 2.4         | 5.8       | v        |                                                 |

| VILHEX           | External Clock<br>Input Low Current                                                      | -0.3        | 0.6       | v        | <u> </u>                                        |

| IHEX             | External Clock<br>Input High Current                                                     |             | 100       | μΑ       | VIHEX = VCC                                     |

| ILEX             | External Clock<br>Input Low Current                                                      |             | 100       | μΑ       | VILEX = VSS                                     |

| VIH              | Input High Level<br>Ports,RESET1, EXT INT1                                               | 2.0         | 5.8       | v        |                                                 |

| VIHOD            | Open Drain Input<br>High Level                                                           | 2.0         | 13.2      | v        |                                                 |

| VIL              | Input Low Level<br>Ports, RESET <sup>1</sup> , EXT INT <sup>1</sup>                      | -0.3        | 0.8       | v        |                                                 |

| Ι <sub>Ι</sub> Γ | Input Low Current<br>Ports, RESET <sup>2</sup> , EXT INT <sup>2</sup>                    |             | -1.6      | mA       | V <sub>IL</sub> =0.4V                           |

| ۱L               | Leakage Current<br>Open drain ports, RAMPRT<br>RESET <sup>3</sup> , EXT INT <sup>3</sup> |             | +10<br>-5 | μΑ       | V <sub>IN</sub> =13.2V<br>V <sub>IN</sub> =0.0V |

| юн               | Output High Current<br>Standard ports, RESET2<br>EXT INT2                                | -100<br>-30 |           | μΑ<br>μΑ | V <sub>OH</sub> =2.4V<br>V <sub>OH</sub> =3.9V  |

|                  |                                                                                          | -0.1        |           | mA       | V <sub>OH</sub> = 2.4V                          |

| OHDD             | OUTPUT High Current                                                                      | -1.5        |           | mA       | V <sub>OH</sub> =1.5V                           |

|                  | Direct Drive Ports                                                                       |             | -8.5      | mA       | V <sub>OH</sub> = 7V                            |

| IOL              | Output Low Current<br>IO ports                                                           | 1.8         |           | mA       | V <sub>OL</sub> =0.4V                           |

| IOHS             | STROBE Output High Current                                                               | -300        |           | μΑ       | V <sub>OH</sub> =2.4V                           |

# DC CHARACTERISTICS (Cont'd)

| SYMBOL | PARAMETER                 | MIN  | МАХ | UNIT | NOTES                                                 |

|--------|---------------------------|------|-----|------|-------------------------------------------------------|

| IOLS   | STROBE Output Low Current | 5.0  |     | mA   | V <sub>OL</sub> = 0.4V                                |

| VIHRPR | RAMPRT Input High Level   | 1.9  | 5.8 | v    | Guaranteed .1V less<br>than V <sub>IH</sub> for RESET |

| VILRPR | RAMPRT Input Low Level    | -0.3 | 0.4 | V    | Guaranteed .1V less<br>than V <sub>IL</sub> for RESET |

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

1. RESET and EXT INT have internal Schmit triggers giving minimum .2V hysteresis.

2. RESET or EXT INT programmed with standard pull-up

3. RESET or EXT INT programmed without standard pull-up

4. Power dissipation for I/O pins is calculated by  $\Sigma(V_{CC} - V_{1L}) (|I_{1L}|) + \Sigma(V_{CC} - V_{OH}) (|I_{OH}|) + \Sigma(V_{OL}) (|I_{OL}|)$

# TIMER AC CHARACTERISTICS

Definitions:

Error = Indicated time value - actual time value

tpsc = t  $\Phi$  x Prescale Value

# Interval Timer Mode:

| Sin       | gle interval error, free running (Note 3) $\ldots$ ±6t $\Phi$                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cu        | mulative interval error, free running (Note 3)                                                                                                                      |

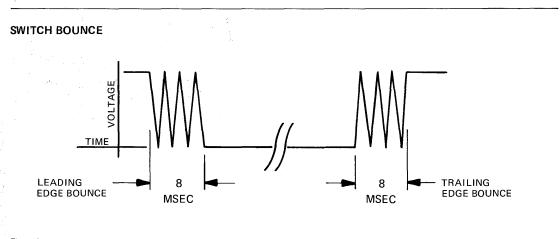

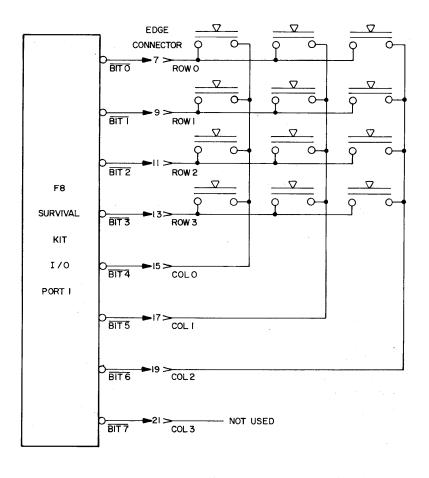

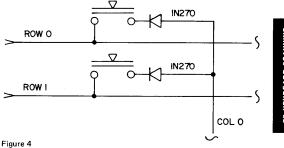

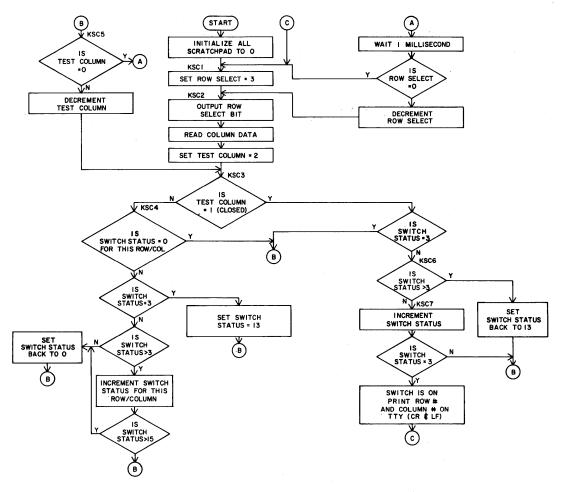

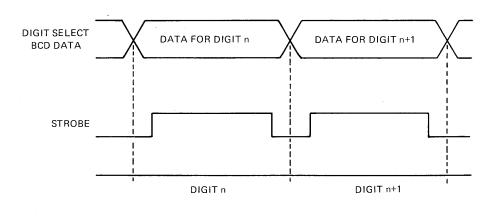

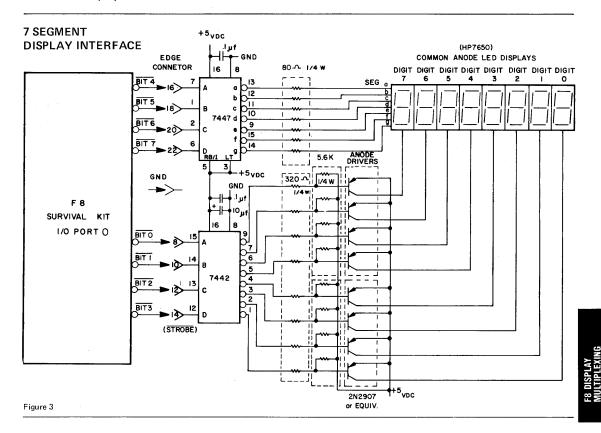

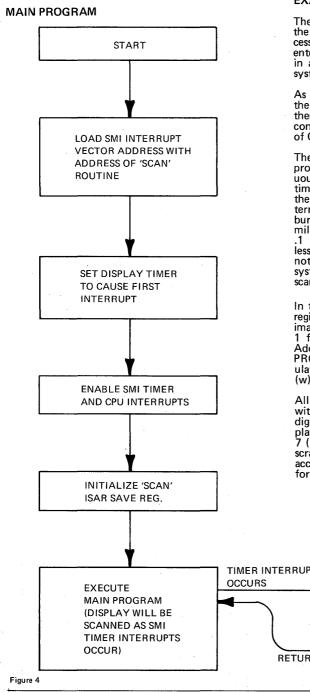

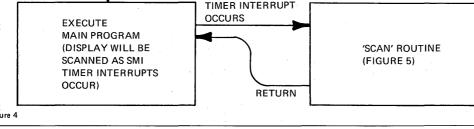

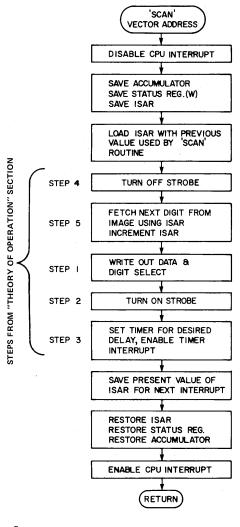

|           | ror between two Timer reads (Note 2). $\ldots$ the two terms $\ldots$ $\ldots$ $\ldots$ $\pm$ (tpsc + t $\check{\Phi}$ )                                            |